# DDVH COURSE FILE

| TECHNOL                                         | LOGY                             |

|-------------------------------------------------|----------------------------------|

| <b>DEPARTMENT OF</b> Electronics an             | nd communications Engineering    |

| (Name of the Subject / Lab Course) : Digita     | al Design Using Verilog HDL      |

| (JNTU CODE ) : A40410                           | Programme : UG                   |

| Branch: ECE                                     | Version No : <i>01</i>           |

| Year: II                                        | Updated on : 17/11/2015          |

| Semester: II                                    | No. of pages :                   |

| Classification status (Unrestricted / Restricte | ed)                              |

| Distribution List :                             |                                  |

| Prepared by :1) Name : B Sreelatha              | 1) Name : T Rama Krishna         |

| 2) Sign :                                       | 2) Sign :                        |

| 3) Design : Assoc. professor                    | 3) Design : Assoc. professor     |

| 4) Date : 17/11/2015                            | 4) Date : 17/11/2015             |

| Verified by : 1) Name :                         | * <u>For Q.C Only.</u> 1) Name : |

| 2) Sign :                                       | 2) Sign :                        |

| 3) Design :                                     | 3) Design :                      |

| 4) Date :                                       | 4) Date :                        |

|                                                 |                                  |

| Approved by : (HOD ) 1) Name :                  |                                  |

| 2) Sign :                                       | 3) Date :                        |

# **Contents required for course file**

- 1. Cover page

- 2. Syllabus copy

- 3. Vision of the Department

- 4. Mission of the Department

- 5. PEOs and POs

- 6. Course objectives and outcomes

- 7. Brief importance of the course and how it fits into the curriculum

- 8. Prerequisites if any

- 9. Instructional Learning Outcomes

- 10. Course mapping with PEOs and POs

- 11. Class Time table

- 12. Individual Time table

- 13. Lecture schedule with methodology being used / adopted

- 14. Detailed notes

- 15. Additional topics

- 16. University previous Question papers of previous years

- 17. Question Bank

- 18. Assignment Questions

- 19. Unit-wise quiz questions and long answer questions

- 20. Tutorial Problems

- 21. Known curriculum Gaps (If any) and inclusion of the same in lecture schedule

- 22. Discussion topics, if any

- 23. References, Journals, websites and E-links if any

- 24. Quality measurement Sheets

- a. Course end survey

- b. Teaching Evaluation

- 25. Students List

- 26. Group-Wise students list for discussion topics

# 2. Syllabus copy

### JAWAHARLAL NEHRU TECHNOLOGIVAL UNIVERSITY HYDERABAD

II Year B.Tech. ECE -II Sem

L T/P/D C 4 -/-/- 4

### **Digital Design using Verilog HDL**

### UNIT I:

**Introduction to Verilog HDL:** Verilog as HDL, Levels of Design Description, Concurrency, Simulation and Synthesis, Functional Verification, System Tasks, Programming Language Interface (PLI), Module, Simulation and Synthesis Tools.

Language Constructs and Conventions: Introduction, Keywords, Identifiers, White Space Characters, Comments, Numbers, Strings, Logic Values, Strengths, Data Types, Scalars and Vectors, Parameters, Operators.

### UNIT II:

**Gate Level Modeling:** Introduction, AND Gate Primitive, Module Structure, Other Gate Primitives, Illustrative Examples, Tri-State Gates, Array of Instances of Primitives, Design of Flip-flops with Gate Primitives, Delays, Strengths and Construction Resolution, Net Types, Design of Basic Circuits. **Modeling at Dataflow Level:** Introduction, Continuous Assignment Structure, Delays and Continuous

Assignments, Assignment to Vectors, Operators.

### UNIT III:

**Behavioral Modeling:** Introduction, Operations and Assignments, Functional Bifurcation, *Initial* Construct, *Always* Construct, Assignments with Delays, *Wait* construct, Multiple Always Blocks, Designs at Behavioral Level, Blocking and Non-Blocking Assignments, The *case* statement, Simulation Flow *if* and *if-else* constructs, *Assign-De-Assign* construct, *Repeat* construct, *for* loop, the *Disable* construct, While loop, Forever loop, Parallel Blocks, Force-Release construct, Event.

### UNIT IV:

**Switch Level Modeling:** Basic Transistor Switches, CMOS Switch, Bi-directional Gates, Time Delays with Switch Primitives, Instantiations with Strengths and Delays, Strength Contention with Trireg Nets, Exercises.

**System Tasks, Functions and Compiler Directives:** Parameters, Path Delays, Module Parameters, System Tasks and Functions, File-Based Tasks and Functions, Computer Directives, Hierarchical Access, User Defined Primitives.

### UNIT V:

**Sequential Circuit Description:** Sequential Models – Feedback Model, Capacitive Model, Implicit Model, Basic Memory Components, Functional Register, Static Machine Coding, Sequential Synthesis.

**Components Test and Verification:** Test Bench- Combinational Circuit Testing, Sequential Circuit Testing, Test Bench Techniques, Design Verification, Assertion Verification.

**TEXT BOOKS:**

1.T.R. Padmanabhan, B. Bala Tripura Sundari , Design through Verilog HDL –, Wiley, 2009. 2.Zainalabdien Navabi, Verilog Digital System Design, TMH, 2<sup>nd</sup> Edition.

### **REFERENCE BOOKS:**

1. Fundamentals of Logic Design with Verilog Design– Stephen. Brown and Zvonko Vranesic, TMH, 2<sup>nd</sup> Edition 2010.

2. Advanced Digital Logic Design using Verilog, State Machine & Synthesis for FPGA – Sunggu Lee, Cengage Learning , 2012.

3. Verilog HDL – Samir Palnitkar, 2<sup>nd</sup> Edition, Pearson Education, 2009.

4. Advanced Digital Design with Verilog HDL – Michael D. Ciletti, PHI, 2009.

# **3. Vision of the Department**

To impart quality technical education in Electronics and Communication Engineering emphasizing analysis, design/synthesis and evaluation of hardware/embedded software using various Electronic Design Automation (EDA) tools with accent on creativity, innovation and research thereby producing competent engineers who can meet global challenges with societal commitment.

# 4. Mission of the Department

- i. To impart quality education in fundamentals of basic sciences, mathematics, electronics and communication engineering through innovative teaching-learning processes.

- ii. To facilitate Graduates define, design, and solve engineering problems in the field of Electronics and Communication Engineering using various Electronic Design Automation (EDA) tools.

- iii. To encourage research culture among faculty and students thereby facilitating them to be creative and innovative through constant interaction with R & D organizations and Industry.

- iv. To inculcate teamwork, imbibe leadership qualities, professional ethics and social responsibilities in students and faculty.

# **5. PEOs and POs**

### **Program Educational Objectives (PEOs):**

- I. To prepare students with excellent comprehension of basic sciences, mathematics and engineering subjects facilitating them to gain employment or pursue postgraduate studies with an appreciation for lifelong learning.

- II. To train students with problem solving capabilities such as analysis and design with adequate practical skills wherein they demonstrate creativity and innovation that would enable them to develop state of the art equipment and technologies of multidisciplinary nature for societal development.

- III. To inculcate positive attitude, professional ethics, effective communication and interpersonal skills which would facilitate them to succeed in the chosen profession exhibiting creativity and innovation through research and development both as team member and as well as leader.

### **Program Outcomes (POs):**

- 1. An ability to apply knowledge of Mathematics, Science, and Engineering to solve complex engineering problems of Electronics and Communication Engineering systems.

- 2. An ability to model, simulate and design Electronics and Communication Engineering systems, conduct experiments, as well as analyze and interpret data and prepare a report with conclusions.

- 3. An ability to design an Electronics and Communication Engineering system, component, or process to meet desired needs within the realistic constraints such as economic, environmental, social, political, ethical, health and safety, manufacturability and sustainability.

- 4. An ability to function on multidisciplinary teams involving interpersonal skills.

- 5. An ability to identify, formulate and solve engineering problems of multidisciplinary nature.

- 6. An understanding of professional and ethical responsibilities involved in the practice of Electronics and Communication Engineering profession.

- 7. An ability to communicate effectively with a range of audience on complex engineering problems of multidisciplinary nature both in oral and written form.

- 8. The broad education necessary to understand the impact of engineering solutions in a global, economic, environmental and societal context.

- 9. A recognition of the need for, and an ability to engage in life-long learning and acquire the capability for the same.

- A knowledge of contemporary issues involved in the practice of Electronics and Communication Engineering profession

- 11. An ability to use the techniques, skills and modern engineering tools necessary for engineering practice.

- 12. An ability to use modern Electronic Design Automation (EDA) tools, software and electronic equipment to analyze, synthesize and evaluate Electronics and Communication Engineering systems for multidisciplinary tasks.

- 13. Apply engineering and project management principles to one's own work and also to manage projects of multidisciplinary nature.

# **6.** Course Objectives and Outcomes

### Course Objectives ( as per JNTU-H)

This course teaches:

- Designing digital circuits, behavioral and RTL modeling of digital circuits using Verilog HDL.

- Verifying these models and synthesizing RTL models to standard cell libraries and FPGAs.

- Students gain practical experience by designing, modeling, implementing and verifying several digital circuits.

This course aims to provide students with the understanding of the different technologies related to HDLs, construct, compile and execute Verilog HDL programs using provided software tools. Design digital components and circuits that are testable, reusable and synthesizable.

### **Course Outcomes**

After the completion of the course, the student would be able to

- CO 1: Describe Verilog hardware description languages (HDL).

- CO 2: Design Digital Circuits.

- CO 3: Write behavioral models of digital circuits.

- CO 4: Write Register Transfer Level (RTL) models of digital circuits.

- CO 5: Verify behavioral and RTL models.

- CO 6: Describe standard cell libraries and FPGAs.

- CO 7: Synthesize RTL models to standard cell libraries and FPGAs.

- CO 8: Implement RTL models on FPGAs and Testing & Verification.

# 7. Brief Importance of the Course and how it fits into the curriculum

a. This is the basic fundamental subject for the programming of the digital Electronics.

b. This subject is required to understand the programming of the combinational and sequential circuit designs.

b. By studying this subject, the students can design and understand digital systems and its importance.

c. The students logical thinking capability will be improved which will help in placements and in their future technical assignments.

## 8. Prerequisites if any

1. Concepts of switching theory and logic design.

# 9. Instructional Learning Outcomes

Learning outcomes are the key abilities and knowledge that will be assessed

### Unit – I:

### **Introduction to Verilog HDL**

- Students understand the importance of HDL (Hardware Descriptive Language) and apply the knowledge of Boolean algebra to design and development digital Systems.

- Understand the difference between concurrent and sequential programming

- ➢ Issues related to simulation and synthesis models.

### Language Constructs and Conventions:

- Knowledge of language constructs

- Pertaining to Semantic and syntactical errors in programming using HDL

- Limitation of HDL

### Unit- II:

### **Gate Level Modeling**

- > Student will learn conventional structural modeling of digital systems.

- Learn to model language defined primitive gates

- > Understand importance component structure in Verilog.

- Learn Hierarchical digital system building

### Modeling at Dataflow Level

Continuous assignment operator based model construction will be learnt.

### Unit – III:

### **Behavioral Modeling:**

- Students will be familiarized to high level abstraction of digital systems with behavioral modeling of systems.

- RTL modeling of digital systems

- ▶ Will be made familiar to behavioral constructs like 'always' ,'initial', 'if', 'if-else', 'case'..etc

- Register and array modeling

### Unit – IV:

### **Switch Level Modeling:**

- > Students will learn low-level abstraction of digital systems.

- Switch level primitives will be learnt

- > Made to familiarize to different strengths of logic values

### System Tasks, Functions and Compiler Directives:

- Understand the importance of system tasks and functions

- Understand compiler directives.

- > Understand user defined primitives and learn to model systems using UDP

- > Learn the intricacies associated with usage of functions and tasks in packages

- > Learn package declaration and package usage in project building

### Unit – V:

### Sequential Circuit Description:

- > Learn to model Sequential circuits at higher level of abstraction using RTL modeling

- > Will be able to design static and dynamic memories

- > Will learn to model in behavioral style of binary encoding and one hot encoding

### **Component Test and Verification:**

- Students understand Test bench generation

- > Producing of test vectors to test the digital systems at higher level of abstraction.

# **10. Course mapping with PEOs and POs**

### Mapping of Course with Programme Educational Objectives:

| 1 | S.No | Course<br>component    | code | course | Semester | PEO 1        | PEO 2        | PEO 3 |

|---|------|------------------------|------|--------|----------|--------------|--------------|-------|

|   | 1    | Digital<br>Electronics |      | DDVH   | 2        | $\checkmark$ | $\checkmark$ |       |

Mapping of Course outcomes with Programme outcomes:

\*When the course outcome weightage is < 40%, it will be given as moderately correlated (1). \*When the course outcome weightage is >40%, it will be given as strongly correlated (2).

| POs                     | 1            | 2            | 3             | 4   | 5 | 6 | 7 | 8            | 9    | 10           | 11           | 12           | 13 |                 |

|-------------------------|--------------|--------------|---------------|-----|---|---|---|--------------|------|--------------|--------------|--------------|----|-----------------|

| DDVH                    | 1            | 2            | 3             | 4   | 5 | 0 | / | 0            | 9    | 10           | 11           | 12           | 15 |                 |

|                         |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| CO 1: Describe Verilog  | N            | $\checkmark$ | $\checkmark$  |     |   |   |   |              |      | $\checkmark$ | $\checkmark$ | N            |    |                 |

| hardware description    |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| languages (HDL).        |              |              | 1             |     |   |   |   |              |      |              |              | 1            |    |                 |

| CO 2: Design Digital    |              | $\checkmark$ | $\mathcal{N}$ |     |   |   |   | V            |      | $\checkmark$ | N            |              |    |                 |

| Circuits.               |              |              |               |     |   |   |   |              |      | ,            |              |              |    |                 |

| CO 3: Write             | $\checkmark$ | $\checkmark$ |               |     |   |   |   |              |      | $\checkmark$ |              |              |    |                 |

| behavioral models of    |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| digital circuits.       |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| CO 4: Write Register    | $\checkmark$ | $\checkmark$ |               |     |   |   |   | $\checkmark$ |      | $\checkmark$ | $\checkmark$ | $\checkmark$ |    | sm              |

| Transfer Level (RTL)    |              |              |               |     |   |   |   |              |      |              |              |              |    | ste             |

| models of digital       |              |              |               |     |   |   |   |              |      |              |              |              |    | Sys             |

| circuits.               |              |              |               |     |   |   |   |              |      |              |              |              |    | Digital Systems |

| CO 5: Verify            |              | $\checkmark$ |               |     |   |   |   | $\checkmark$ |      |              |              | $\checkmark$ |    | git             |

| behavioral and RTL      |              |              |               |     |   |   |   |              |      |              |              |              |    | Di              |

| models.                 |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| CO 6: Describe          | $\checkmark$ |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| standard cell libraries |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| and FPGAs.              |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| CO 7: Synthesize RTL    | $\checkmark$ |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| models to standard cell |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| libraries and FPGAs.    |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| CO 8: Implement RTL     |              | $\checkmark$ |               |     |   |   |   | $\checkmark$ |      | $\checkmark$ |              |              |    |                 |

| models on FPGAs and     |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

| Testing & Verification. |              |              |               |     |   |   |   |              |      |              |              |              |    |                 |

|                         | 1.           | i T          | mo            | tah |   | f |   |              | ad a | loco         |              |              |    |                 |

**<u>11.Time table of concerned class</u>**

# **<u>12. Individual time table</u>**

| SL.<br>NO | Unit<br>No. | Total<br>no. of<br>peroi<br>ds | Date | Topics to be covered in one<br>lecture                                                                                        | Regula<br>r/<br>Additio<br>nal | Teaching<br>aids used<br>LCD/<br>OHP/ BB | Rema<br>rks |

|-----------|-------------|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------|-------------|

| 1         | I           | 6                              |      | Verilog as HDL, Levels of<br>Design Description, Concurrency,<br>Verilog as HDL, Levels of<br>Design Description              | Regular                        | OHP,BB                                   |             |

| 2         |             |                                |      | Concurrency Simulation and<br>Synthesis, Functional<br>Verification, System Tasks,<br>Programming Language Interface<br>(PLI) | Regular                        | OHP,BB                                   |             |

| 3         |             |                                |      | Module, Simulation and<br>Synthesis Tools<br>LANGUAGE CONSTRUCTS<br>AND CONVENTIONS<br>Introduction, Keywords                 | Regular                        | OHP,BB                                   |             |

| 4         |             |                                |      | Identifiers, White Space<br>Characters, Comments, Numbers,<br>Strings, Logic Values, Strengths                                | Regular                        | BB                                       |             |

| 5         |             |                                |      | Data Types, Scalars and Vectors,<br>Parameters, Memory, Operators,<br>System Tasks, Exercises.                                | Regular                        | OHP,BB                                   |             |

| 6         |             |                                |      | Tutorial class-1                                                                                                              |                                | BB                                       |             |

| 7         | II          | 11                             |      | Introduction, AND Gate<br>Primitive, Module Structure                                                                         | Regular                        | OHP,BB                                   |             |

| 8         |             |                                |      | Other Gate Primitives, Illustrative                                                                                           | Regular                        | OHP,BB                                   |             |

# **<u>13. Lecture schedule with methodology being used / adopted</u>**

11

|    |     |   | Examples, Tri-State Gates                                                                                                               |                |        |

|----|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|

| 9  |     |   | Array of Instances of Primitives,<br>Additional Examples                                                                                | Regular        | OHP,BB |

| 10 |     |   | Design of Flip-flops with Gate<br>Primitives, Delays, Strengths and<br>Contention Resolution                                            | Regular        | BB     |

| 11 |     |   | Net Types, Design of Basic<br>Circuits, Exercises.                                                                                      | Regular        | BB     |

| 12 |     |   | Verilog designs for various<br>rounding methods                                                                                         | Additio<br>nal | OHP,BB |

| 13 |     |   | Introduction, Continuous<br>Assignment Structures, Delays<br>and Continuous Assignments                                                 | Regular        | OHP,BB |

| 14 |     |   | Assignment to Vectors,<br>Operators.                                                                                                    | Regular        | OHP,BB |

| 15 |     |   | Tutorial class-2                                                                                                                        |                | BB     |

| 16 |     |   | Solving University papers                                                                                                               |                | BB     |

| 17 |     |   | Assignment test-1                                                                                                                       |                | BB     |

| 18 | III | 6 | Introduction, Operations and<br>Assignments, Functional<br>Bifurcation, <i>Initial</i> Construct,<br><i>Always</i> Construct, Examples  | Regular        | OHP,BB |

| 19 |     |   | Assignments with Delays, <i>Wait</i><br>construct, Multiple Always<br>Blocks, Designs at Behavioral<br>Level                            | Regular        | OHP,BB |

| 20 |     |   | <br>Blocking and Non blocking<br>Assignments, The <i>case</i> statement,<br>Simulation Flow. <i>if</i> and <i>if-else</i><br>constructs | Regular        | OHP,BB |

| 21 |    |    | <i>assign-deassign</i> construct, <i>repeat</i><br>construct, <i>for</i> loop, the <i>disable</i><br>construct | Regular        | OHP,BB |

|----|----|----|----------------------------------------------------------------------------------------------------------------|----------------|--------|

| 22 |    |    | <i>while</i> loop, <i>forever</i> loop, parallel<br>blocks, <i>force-release</i> construct,<br>Event.          | Regular        | BB     |

| 23 |    |    | Tutorial class-3                                                                                               |                | BB     |

| 24 | IV | 12 | SWITCH LEVEL MODELING.<br>Introduction Basic Transistor<br>Switches, CMOS Switch, Bi-<br>directional Gates     | Regular        | OHP,BB |

| 25 |    |    | Time Delays with Switch<br>Primitives, Instantiations with<br>Strengths and Delays                             | Regular        | BB     |

| 26 |    |    | .Strength Contention with Trireg<br>Nets, Exercises.                                                           | Regular        | BB     |

| 27 |    |    | Combinational synthesis                                                                                        | Additio<br>nal | OHP,BB |

| 28 |    |    | Tutorial calss-4                                                                                               |                | BB     |

| 29 |    |    | Solving university papers                                                                                      |                | BB     |

| 30 |    |    | Assignment test-2                                                                                              |                |        |

| 31 |    |    | Mid test-1                                                                                                     |                |        |

| 32 |    |    | Introduction, Parameters, Path<br>Delays, Module Parameters,<br>System Tasks and Functions                     | Regular        | OHP,BB |

| 33 |    |    | File-Based Tasks and Functions,<br>Compiler Directives, Hierarchical<br>Access,                                | Regular        | OHP,BB |

| 34 |    |    | User- Defined Primitives (UDP)                                                                                 | Regular        | OHP,BB |

| 35 |    |    | Tutorial class-5                                                                                               |                | BB     |

| 36 | V | 11 | Sequential Models – FeedBack<br>Model, Capacaitive Model,<br>Implicit Model       | Regular | OHP,BB |

|----|---|----|-----------------------------------------------------------------------------------|---------|--------|

| 37 |   |    | Basic Memory Components,<br>Functional Register                                   | Regular | OHP,BB |

| 38 |   |    | Static Machine Coding                                                             | Regular | OHP,BB |

| 39 |   |    | Sequential Synthesis                                                              | Regular | OHP,BB |

| 40 |   |    | Tutorial class – 6                                                                |         | BB     |

| 41 |   |    | Component Test and Verification:<br>Test Bench – Combinational<br>Circuit Testing | Regular | ОНР,ВВ |

| 42 |   |    | Test Bench – Sequential Circuit<br>Testing                                        | Regular | OHP,BB |

| 43 |   |    | Test Bench Techniques                                                             | Regular | OHP,BB |

| 44 |   |    | Design Verification                                                               | Regular | OHP,BB |

| 45 |   |    | Assertion Verification                                                            | Regular | OHP,BB |

| 46 |   |    | Tutorial Class – 7                                                                |         | BB     |

| 47 |   |    | Solving university papers                                                         |         | BB     |

| 48 |   |    | Assignment test-2                                                                 |         |        |

| 49 |   |    | Mid test-2                                                                        |         |        |

# **14. Detailed Notes**

### <u>UNIT 1</u>

### **INTRODUCTION TO VERILOG**

### VERILOG AS HDL:

Verilog HDL is a hardware description language used to design and document electronic systems. Verilog HDL allows designers to design at various levels of abstraction.

• Why use an HDL?

- Describe complex designs (millions of gates)

- Input to synthesis tools (synthesizable subset)

- Design exploration with simulation

- Why not use a general purpose language

- Support for structure and instantiation (objects?)

- Support for describing bit-level behavior

- Support for timing

- Support for concurrency

- Verilog vs. VHDL

- Verilog is relatively simple and close to C

- VHDL is complex and close to Ada

- Verilog has 60% of the world digital design market (larger share in

US)

- Verilog modeling range

- From gates to processor level

- We'll focus on RTL (register transfer level)

### LEVELS OF DESIGN DESCRIPTION:

For the design of a digital system using an automated design environment, the design flow begins with specification of the design at various levels of abstraction and ends with generating net list for an application specific integrated circuits (ASIC), layout for a custom IC, or a program for programmable logic devices (PLD). Figure 1.1 shows steps involved in this design flow.

In the design entry phase, a design is specified as a mixture of behavioral Verilog code, instantiation of Verilog modules, and bus and wire assignments. A design engineer is also responsible for generating test benches. for his or her design for verification of the design and later for verifying the synthesis output. Design verification can be done by simulation, assertion verification, formal verification, or a mix of all three. After performing this design validation phase (this is called the pre synthesis verification), this design is taken through the synthesis process to translate it into actual hardware of a target device. Here, target device refers to the specific field programmable logic device (FPLD) that is being programmed, the ASIC that is being manufactured by an outside source, or the custom IC that is being fabricated. After the

synthesis process and before the actual hardware is generated, another simulation, which is referred to as posts synthesis simulation, is done. This simulation can take advantage of the same test bench generated for the Verilog model of the system before it is synthesized. This way, the behavioral model of the design and its hardware model are tested with the same data. The difference between pre- and posts synthesis simulations is in the level of details obtained from each simulation.

### **CONCURRENCY:**

It is desired that all the elements present in an electronic circuit must be active and function simultaneously as their voltages and current may vary at the same instant. Even, there is a possibility to change their logic state. Multiple activities that are distributed among various modules need to be run concurrently. Hence simulators are designed to carry out concurrent simulation. Simulation done at uniform time intervals obtains concurrency.

Like timing, concurrency is an essential feature of any language for description of hardware. When a software programmer develops code for performing a certain task, he or she thinks of this task in a sequential manner. The software developed this way will have a top down sequential flow. On the other hand, when a hardware designer or modeler is to describe a hardware system, he or she thinks of this hardware as interconnections of components. The functionality of the overall system is achieved by concurrently active components communicating through their input and output ports.

The functionality of each component may be described by concurrent subcomponents or described by a program in a sequential manner.

We refer to concurrency as the way the simulation of components or constructs appears to the user. Obviously, Verilog is a language for which simulators have been developed on single-processor platforms, and true concurrency in the execution of thousands of components cannot exist. Through the use of concurrent constructs, timing of interconnecting signals, and order of simulation of constructs or components, a Verilog simulator makes us (the users) think that such execution is being done concurrently.

### SIMULATION AND SYNTHESIS, tools:

Simulation for design validation is done before a design is synthesized. This simulation pass is also referred to as behavioral, RT level, or pre synthesis simulation. At the RT level a design includes clock-level timing but no gate and wire delays are included. Simulation at this level is accurate to the clock level. Timing of RT-level simulation is at the clock level and does not usually consider hazards, glitches, race conditions, setup and hold violations, and other detailed timing issues. The advantage of this simulation is its speed compared with simulations at the gate or transistor levels.

Simulation of a design requires test data, and usually Verilog simulation environments provide various methods for application of these data to the design being tested. Test data can be generated graphically using waveform editors, or through a test bench. For simulating with a Verilog test bench, the test bench

instantiates the design under test, and as part of the code of the test bench it applies test data to the instantiated circuit.

Synthesis is the process of automatic hardware generation from a design description that has an unambiguous hardware correspondence. A Verilog description for synthesis cannot include signal and gate level timing specifications, file handling, and other language constructs that do not translate to sequential or combinational logic equations. Furthermore, Verilog descriptions for synthesis must follow certain styles of coding for combinational and sequential circuits. These styles and their corresponding Verilog constructs are defined under Verilog for RTL synthesis. In the design process, after a design is successfully entered and its Pre synthesis simulation results have been verified by the designer, it must be compiled to make it one step closer to an actual hardware on silicon. This design phase requires specification of the hardware that the design is to be realized in.

For example, we have to specify a specific ASIC, or a field programmable gate array (FPGA) part as our "target hardware." When the target hardware is specified, technology files of that hardware (ASIC, FPGA, or custom IC) with detailed timing and functional specification become available to the compilation process. The compilation process, translates various parts of the design to an intermediate format (analysis phase), links all parts together, generates the corresponding logic (synthesis phase), places and routes components of the target hardware, and generates timing details.

### FUNCTIONAL VERIFICATION:

Testing is done by two measurements namely:

- 1. Functional test

- 2. Timing test

It does both the measurements. Usually a test bench is provided for a design that is to be tested. Today's functional verification flow mainly contains following steps:

- 1.Generate the stimulus vectors.

- 2.Send the Stimulus to the DUT.

- 3. Monitor the response generated by the DUT.

- 4. Verify the response generated.

- 5. Generate report about the DUT performance.

- 6. Some kind of feedback to show the quality of test bench

### SYSTEM TASKS:

For test bench generation, data input and output, timing check, simulation flow control, data conversion, and memory initialization. Verilog provides a number of system tasks and functions categorized into ten groups. The names of system tasks and functions begin with a dollar sign (\$), followed by a task

specified. The name of the task or function usually contains characters and names that describe its functionality.

### **Display tasks**

Display tasks are used for outputting to the standard output device. The most basic display task is the \$display task, which writes its string argument to the display device. Other tasks include those for monitoring and outputting variable values as they change (the \$monitor group of tasks) and those for displaying variables at a selected time (the \$display tasks). Display tasks can display in binary, hexadecimal, or octal formats. The character b, h, or o at the end of the task name specifies the data type a task handles. For all display tasks, a generic task can be used to display data with specified formats and data types.

### File I/O tasks

File output tasks begin with a dollar sign followed by the letter f (for file) and then by the same task names as those of the display tasks. These tasks perform the same functionalities as their display task counterparts, except that their output is to a file instead of to the display terminal. The \$fopen function opens a file and assigns an integer file description. The file descriptor will be used as an argument for all file I/O tasks. In addition, there are string write tasks (\$swrite) that write their formatted outputs to a string. Verilog also provides tasks for inputting data from files or strings. Such tasks allow reading characters, formatted data, or complete memory data from external data files or declared strings. Examples of these tasks are \$fgetc, \$fscanf, and \$sscanf for getting a character from a file, reading formatted data from a file, and reading formatted data from a string, respectively. Other input tasks exist for reading memory data directly intoa declared memory. Examples of such tasks are \$fread and \$readmemh. File positioning tasks, \$fseek and \$frewind are also available for positioning file pointer for read or write. Verilog I/O tasks are useful in developing complete hardware/software environments and developing test benches.

### **Timescale tasks**

Timescale tasks are \$printtimescale and \$timeformat. The \$printtimescale task displays the timescale and precision of the module whose hierarchical name is being passed to it as its argument. The \$timeformat task formats time for display by file IO and display tasks.

### Simulation control tasks

Simulation control tasks are \$finish and \$stop. The \$finish task ends the simulation and exits. Usually, simulation environments require a confirmation before the action of exiting the environment is taken. The \$stop task suspends the simulation and does not exit the simulation environment.

### Timing check tasks

Timing check tasks are used for checking timings, such as pulse width duration and setup and hold times. In general, timing check tasks check the timing on one signal or the relative timing of several signals for certain conditions to hold. If a violation is detected, a message will be issued in the user simulation environment display area. For example, the statement shown below uses the \$nochange timing check task to report a violation if d\_input changes in the period of three time units before and five time units after the positive edge of the clock.

\$nochange (posedge clock, d\_input, 3, 5);

### **PROGRAMMING LANGUAGAE INTERFACE :**

After finishing the compilation of a Verilog module, a dynamic interface is provided by the PLI that increases the scope of Verilog, so it can be linked with C program.

### MODULE:

- The module is the basic building block in Verilog

- Modules can be interconnected to describe the structure

of your digital system

- Modules start with keyword module and end with

keyword end module.

### **Module Ports**

- Similar to pins on a chip

- Provide a way to communicate with outside world

- Ports can be input, output or in out.

A module is the main structure for definition of hardware components and test benches. Modules begin with the module keyword and end with end module. Immediately following the module keyword, port list of the module appears enclosed in parenthesis. Declaration of mode, type, and size of ports can either appear in the port list or as separate declarations.

Example:

module FlipFlop (preset, reset, din, clk, qout);

input preset, reset, din, clk;

output qout;

reg qout;

```

always @ (posedge clk) begin

if (reset) qout <= #7 0;

else if (preset) qout <= #7 1;

else qout <= #8 din;

end

end module

```

The body of a module consists of the specification of the operation of the hardware the module is representing. A test bench module has no ports. It instantiates the module under test (MUT) and through the use of concurrent statements or procedural blocks applies data to the ports of MUT. Multiple modules can be tested with the same test bench.

### **TEST BENCHES:**

Values assigned to inputs of a circuit for examining its operation are either specified within a simulation environment using a waveform editor, or by a Verilog test bench. In this description, TriMux is instantiated

`timescale 1ns/100ps

module TriMuxTest;

reg i0=0, i1=0, s=0;

wire y;

TriMux MUT (i0, i1, s, y);

initial begin

#15 i1=1'b1;

#15 s=1'b1;

#15 s=1'b0;

#15 i0=1'b1;

#15 i0=1'b0;

#15 \$finish;

end

end module

The initial statement is a procedural construct and uses delay control statements to delay the program flow in this procedural block. After each such delay, a value is assigned to i0, i1, or s. At the end of this block, after a 15-ns delay, the \$finish simulation control task finishes the simulation run. The delay before \$finish allows the last input change to have a chance to affect the circuit output. The delay values (15 ns) used in this example are chosen so that inputs remain stable while a change is propagating through the circuit.

### LANGUAGE CONSTRUCTS AND CONVENTIONS:

### Keywords:

Every language has some keywords reserved for certain use. They describe the language constructs. In Verilog there are many keywords. Few of them are:

- 1. Module: a module is defined starting with this keyword.

- 2. End module: a module is ended with this definition

- 3. **Begin**: a set of statements in a block start with this keyword.

- 4. End: a set of statements within the block are terminated with this word.

- 5. If : verifies conditional statements.

### **IDENTIFIERS:**

Identifiers are names that are given to elements such as modules, registers, ports, wires, instances, and procedural blocks. An identifier is any sequence of letters, digits, and the underscore (\_) symbol except that:

the first character must not be a digit, and the identifier must be 1024 characters or less.

**Verilog is case sensitive**, ie Upper and lower case letters are considered to be different. System tasks and system functions are identifiers that always start with the dollar symbol. Escaped identifiers allow for any printable ASCII character to be included in the name. Escaped identifiers begin with white space. The backslash ("\") character leads off the identifier, which is then terminated with white space. The leading backslash character is not considered part of the identifier.

Examples of escaped identifiers include:

\flip-flop

a+b

Escaped identifiers are used for translators from other CAD systems. These systems may allow special characters in identifiers. Escaped identifiers should not be used under normal circumstances.

### WHITE SPACE CHARACTERS & COMMENTS:

White space is defined as any of the following characters: blanks, tabs, newlines, and form feeds. These are ignored except for when they are found in strings.

There are two forms of comments. The single line comment begins with the two characters

### // and ends with a new-line.

A block comment begins with the two characters /\* and ends with the two characters \*/. Block comments may span several lines. However, they may not be nested.

### NUMBERS:

Constants in Verilog are integer or real. Specification of integers can include X (or x) and Z (or z) in addition to the standard 0 and 1 logic values. Integer formats provide various ways for representing bit streams. Integers may be sized or un sized. A sized integer begins with the number of equivalent bits, followed by the single quote character ('), a base specifier, and the digits of the number in the specified base. The base specifier is a single lower or uppercase character, b, d, o, or h for binary, decimal, octal, and hexadecimal bases. The general format for integers is: number of bits 'base identifier digits

Digits in the decimal (d) system are 0 through 9. For hexadecimal, octal, and binary systems, in addition to their standard digits, X and Z (both upper and lowercase) characters are also allowed. Hexadecimal and octal X and Z digits expand to 4 or 3 bits of X and Z respectively. A number without the number\_of\_bits specification is regarded as an un sized number

`timescale 1ns/100ps

module NumberTest;

reg [11:0] a = 8'shA6; initial \$displayb ("a=", a);

// a=111110100110

reg [11:0] b = 8'sh6A; initial \$displayb ("b=", b);

// b=000001101010

reg [11:0] c = 'shA6; initial \$displayb ("c=", c);

// c=000010100110

reg [11:0] d = 'sh6A; initial \$displayb ("d=", d);

// d=000001101010

reg [11:0] e = -8'shA6; initial \$displayb ("e=", e);

// e=000001011010

reg [11:0] f = -'shA6; initial \$displayb ("f=", f);

// f=111101011010

```

reg [11:0] g = 9'shA6; initial $displayb ("g=", g);

```

// g=000010100110

reg [11:0] h = 9'sh6A; initial \$displayb ("h=", h);

// h=000001101010

reg [11:0] i = -9'shA6; initial \$displayb ("i=", i);

// i=111101011010

reg [11:0] j = -9'sh6A; initial \$displayb ("j=", j);

// j=111110010110

reg [11:0] k = 596; initial \$displayb ("k=", k);

// k=001001010100

reg [11:0] l = -596; initial \$displayb ("l=", l);

### // l=110110101100

Endmodule

### STRINGS:

The strings in Verilog are sequences of 8-bit ASCII characters enclosed within quotation marks.

"This is an example"

As mentioned before white spaces are not ignored inside this string. There is no special data type available to store strings. reg should be used to store the stings. Above string example has 18 characters (including white spaces) so it nees following variable to store the completer string

reg[8\*[18-1]:0] a;

Now 'a' can hold the above string

a = "This is an example";

If you wan to include special characters like quotes(") you must use escape sequence.

```

text = "\"vlsi-world.com\"";

text1 = "vlsi-world.com";

```

text will produce "vlsi-world.com" text1 will produce vlsi-world.com

Use \t to insert tabs \n to insert new lines \\ to insert \ character \" to insert " character

### **LOGIC VALUES :**

0: zero, logic low, false, ground

- 1: one, logic high, power

- X: unknown

- Z: high impedance, unconnected, tri-state

Bit type, or bits of vectors or arrays, of Verilog wires and variables take the 4-value logic value system. Values in this system are 0, 1, Z, and X. The 0 value represents forcing 0 like a direct pull to the ground, or a resistive 0, or a capacitive 0. A resistive 0 is generated when there is a

large resistance between a line and a forcing 0 value. A capacitive 0 is when a line is float; but has a capacitance that has a zero charge. The 1 value represents forcing 1, resistive 1, and a capacitive 1. These are defined similar to various modes of the 0 value. For example a forcing 1 is defined as the logic value driven by a supply voltage. The Z value represents an undriven, high-impedance value. This is the

electrical float which causes no current flow to either supply or ground voltage. Both Z and z are acceptable forms of this logic value. The X value represents a conflict in multiple driving values, an unknown, an uninitialized value, a short between two opposing values (0 and 1), or a bus contention. Driven wires and Verilog variables assume X for their initial values. Figure 3.5 shows several examples for the four values of Verilog's logic value system. Both X and x are acceptable forms of this logic value.

### STRENGTHS:

The strength declaration construct is used for modeling net type variables for a close correspondence with physical wires.

(Strength1, Strength0) (Strength0, Strength1) Strength1: supply1, strong1, pull1, large1, weak1, medium1, small1, highz1 Strength0: supply0, strong0, pull0, large0, weak0, medium0, small0, highz0

Strengths can be used to resolve which value should appear on a net or gate output.

There are two types of strengths: drive strengths (*Example 1*) and charge strengths (*Example 2*). The drive strengths can be used for nets (except **trireg** net), gates, and UDPs. The charge strengths can be used only for **trireg** nets. The drive strength types are **supply**, **strong**, **pull**, **weak**, and **highz** strengths. The charge strength types are **large**, **medium** and **small**strengths.

All strengths can be ordered by their value. The **supply** strength is the strongest and the **highz** strength is the weakest strength level. Strength value can be displayed by system tasks (**\$display**, **\$monitor** - by using of the %v characters - see Display tasks for more explanation).

| Strength | Value | Value displayed by display tasks |

|----------|-------|----------------------------------|

| supply   | 7     | Su                               |

| strong   | 6     | St                               |

| pull     | 5     | Pu                               |

| large    | 4     | La                               |

| weak     | 3     | We                               |

| medium   | 2     | Ме                               |

| small    | 1     | Sm                               |

| highz    | 0     | HiZ                              |

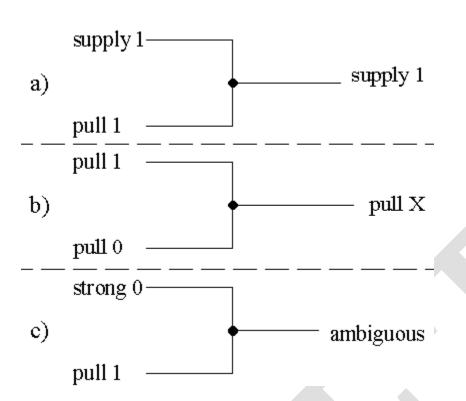

f two or more drivers drive a signal then it will have the value of the strongest driver (*Example 3*).

If two drivers of a net have the same strength and value, then the net result will have the same value and strength (*Example 4*).

If two drivers of a net have the same strength but different values then signal value will be unknown and it will have the same strength as both drivers (*Example 5*).

If one of the drivers of a net has an H or L value, then signal value will be n1n2X, where n1 is the strength value of the driver that has the smaller strength, and n2 is strength value of driver that has the larger strength (*Example 6*).

The combinations (highz0, highz1) and (highz1, highz0) are illegal.

### DATA TYPES:

Verilog has net and reg data types representing wires and variables,

respectively. The net type represents data carriers such as interconnecting wires, gate outputs, and busses. The reg data type represents

variables that hold the value they are assigned until they are overwritten. Additionally, a net or a reg can be declared as signed, which determines how they interpret data assigned to them

• Nets

- Nets are physical connections between devices

- Nets always reflect the logic value of the driving device

- Many types of nets, but all we care about is wire

- Registers

- Implicit storage unless variable of this type is

- modified it retains previously assigned value

- Does not necessarily imply a hardware register

- Register type is denoted by reg

- int is also used

### SCALARS AND VECTORS :

Vectors are multiple bit widths net or reg data type variables that can be declared by specifying their range.

Syntax:

### net\_type [msb:lsb] list\_of\_net\_identifiers;

### reg [msb:lsb] list\_of\_register\_identifiers;

Vector range specification contains two constant expressions: the msb (most significant bit) constant expression, which is the left-hand value of the range and the lsb (least significant bit) constant expression, which is the right-hand value of the range. The msb and lsb constant expressions should be separated by a colon.

Both the msb constant expression and the lsb constant expression can be any value - positive, negative, or zero. The lsb constant expression can be greater, equal or less than the msb constant expression.

Vectors can be declared for all types of **net** data types and for **reg** data types. Specifying vectors for **integer**, **real**, **realtime**, and **time** data types is illegal.

Vector nets and registers are treated as unsigned values (see: Arithmetic expressions with registers and integers for more explanations).

- Both the msb and the lsb expressions should be constant expressions.

- The msb and the lsb constant expressions may be positive, negative, or zero.

- The lsb constant expression may be greater, equal or less than the msb constant expression.

- Vectors can be declared only for **nets** and **reg** data types.

- Vector declaration for integer, real, realtime, and time data types are illegal.

### PARAMETERS:

Parameters are constants typically used to specify the width of variables and time delays.

Syntax :

### **parameter** identifier = constant\_expression,

identifier = constant\_expression ;

### **defparam** hierarchical\_path = constant\_expression ;

In Verilog HDL, parameters are constants and do not belong to any other data type such as net or register data types.

A constant expression refers to a constant number or a previously defined parameter .You are not allowed to modify parameter values at runtime, but you can modify a parameter value using the **defparam** statement. The defparam statement can modify parameters only at the time of compilation. Parameter values can also be modified using #delay specification with module instantiation.

In Verilog there are two ways to override a module parameter value during a module instantiation. The first method is by using the *defparam* keyword and the second method is called *module instance parameter value assignment*.

After the *defparam* keyword, the hierarchical path to the parameter is specified along with the new value of the parameter. In this case, the new value should be a constant expression. If the right-hand side expression references any parameters it should be declared within the module where defparam is invoked.

The *module instance parameter value assignment* method looks like an assignment of delay to gate instance .This method overrides parameters inside instantiated modules, in the order, that they appear in the module. Using this format, parameters cannot be skipped.

Constant expressions can contain previously declared parameters. When changes are detected on the previously declared parameters, all parameters that depend on this value are automatically updated.

Example :

module top; reg Clk ; reg [7:0] D ; wire [7:0] Q ; my\_module inst\_1(Clk, D, Q) ; endmodule

module override ;

defparam top.inst\_1.width = 7 ;

endmodule

- Parameters are constants.

- If you are using the defparam statement, remember that you have to specify a hierarchical path to your parameter.

- You cannot skip over a parameter in a *module instance parameter value assignment*. If you need do this, use the initial value for parameter that is not to be overwritten.

- When one parameter depends on the other, remember that if you change the first one, the second will automatically be updated.

### **MEMORIES:**

Memories are arrays of registers.

### SYNTAX :

reg memory\_width memory\_identifier memory\_depth;

### integer memory\_identifier memory\_length;

time memory\_identifier memory\_length;

Memories can be declared only for **reg**, **integer** and **time** data types. Depth of memory should be declared by specifying a range following the memory identifier . Registers and memories can be declared in the same line .Elements of memory type can be accessed by memory index . An assignment to a memory identifier without specified memory index is illegal. Bit-selects and part-selects on memory elements are not allowed. If access to individual bits of memory is needed, then a word containing that bit should be assigned to a register with the same width. All operations should then be done on this register and the result should be assigned back to the memory word . Memory words can be accessed individually, but bit-select and part-select operations cannot be done on memories or memory words directly.

Vector declaration and memory declaration are not the same. If a variable is declared as a vector, all bits can be assigned a value in one statement. If a variable is declared as memory then a value to each element should be assigned separately.

**reg** [7:0] vect; **reg** array[7:0]; vect = 8'b11001010; array[7] = 1'b1; array[6] = 1'b1; array[5] = 1'b0; array[4] = 1'b0; array[3] = 1'b1; array[2] = 1'b0; array[1] = 1'b1; array[0] = 1'b0;

- Memories can be declared only for **reg**, **integer** and **time** registers types.

- Bit-selects and part-selects on memory elements are prohibited.

### **OPERATORS** :

Operators provide a means to construct expressions.

### Syntax :

Arithmetic: + - \* /

Modulus: %

Relational:  $<\!<=>>=$

Logical: ! && ||

Logical equality: == !=

Case equality: === !==

Bit-wise: ~ & | ^ ~^ ~~

Reduction: & ~& | ~| ^ ~^ ^~

Shift: << >>

Conditional: ?:

Event or: or

Concatenations: { } { { } }

Verilog HDL operators can be divided into several groups.

| Operator      | Description          |

|---------------|----------------------|

| + - ! ~       | Unary                |

| * / %         | Arithmetic           |

| + - (binary)  | Binary               |

| <<>>>         | Shift                |

| < <= > =>     | Relational           |

| == != === !== | Equality             |

| & ~&          | and nand             |

| ^ ~^ ^~       | xor xnor             |

| ~             | or nor               |

| &&            | Logical and          |

|               | Logical or           |

| ?:            | Conditional operator |

### Table 13: Operator's priority

### Arithmetic operators

The arithmetic operators can be used with all data types.

| Operator | Description            |

|----------|------------------------|

| a + b    | a <b>plus</b> b        |

| a - b    | a <b>minus</b> b       |

| a * b    | a <b>multiply by</b> b |

| a / b    | a <b>divide by</b> b   |

| a % b    | a <b>modulo</b> b      |

### **Table 14: Arithmetic operators**

The modulus operator is not allowed for real data type variables. For the modulus operator, the result takes the sign of the first operand.

### **Relational operators**

The relational operators are used to compare expressions. The value returned by the relational operators is 0 if the expression evaluates to false and 1 if expression evaluates to true.

| Operator | Description                      |

|----------|----------------------------------|

| a < b    | a <b>less than</b> b             |

| a > b    | a greater than b                 |

| a <= b   | a <b>less than or equal to</b> b |

| a => b   | a greater than or equal to b     |

### **Equality operators**

The equality operators are used to compare expressions. If a comparison fails, then the result will be 0, otherwise it will be 1.

If both operands of logical equality (==) or logical inequality (!=) contain unknown (x) or a high-impedance (z) value, then the result of comparison will be unknown (x). Otherwise it will be true or false.

If operands of case equality (===) or case inequality (!==) contain unknown (x) or a high-impedance (z) value, then the result will be calculated bit by bit.

Examples of using the equality operators are shown in .

### **Logical operators**

The logical operators are used to connect expressions.

| Operator | Description    |

|----------|----------------|

| a && b   | a <b>and</b> b |

| a    b   | a <b>or</b> b  |

| !a not a |

|----------|

|----------|

The result for these operators is 0 (when false), 1 (when true), and unknown (x - when ambiguous). The negation operator (!) turns a nonzero or true value of the operand into 0, zero or false value into 1, and ambiguous value of operator results in x (unknown value).

### **Bit-wise operators**

The bit-wise operators calculate each bit of results by evaluating the logical expression on a pair of corresponding operand bits.

| & | 0 | 1 | X | Z |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | X | X |

| X | 0 | x | х | X |

| Z | 0 | X | х | X |

### **Bit-wise and operator**

|   | 0 | 1 | x | Z |

|---|---|---|---|---|

| 0 | 0 | 1 | х | X |

| 1 | 1 | 1 | 1 | 1 |

| х | х | 1 | X | X |

| Z | X | 1 | X | X |

### **Bit-wise or operator**

| ^ | 0 | 1 | х | Z |

|---|---|---|---|---|

| 0 | 0 | 1 | X | x |

| 1 | 1 | 0 | x | X |

| X | х | X | х | x |

| Z | х | X | x | X |

### Bit-wise exclusive or operator

| ~^ ^~ | 0 | 1 | x | z |

|-------|---|---|---|---|

| 0     | 1 | 0 | x | X |

| 1     | 0 | 1 | x | X |

| Х     | X | x | x | X |

| Z     | X | X | x | X |

### Bit-wise exclusive nor operator

| ~ | Result |

|---|--------|

| 0 | 1      |

| 1 | 0      |

| Х | X      |

| Z | X      |

### **Bit-wise negation operator**

### **Reduction operators**

The reduction operator produces a 1-bit result. This result is calculated by recursively applying bit-wise operation on all bits of the operand. At each step of this recursive calculation the logical bit-wise operation is performed on the result of a previous operation and on the next bit of the operand. The operation is repeated for all bits of the operand.

### **Shift operators**

The shift operators perform left and right shifts on their left operand by the number of positions specified by their right operand. All vacated bits are filled with zeroes. If the expression that specifies the number of bits to shift (right operand) has unknown (x) or high-impedance (z) value, then result will be unknown.

### **Conditional operator**

The conditional operator is described in the Conditional operator section.

### Concatenations

Concatenations are described in the Concatenations section.

### **Event or operator**

The event or operator is described in the section on Procedural timing controls.

### UNIT II

### **GATE LEVEL MODELLING**

### **INTRODUCTION:**

The previous section discussed the role of wires and basics of generating Verilog modules for simulation. Building upon that material, this section presents generation of Verilog modules using predefined gate primitives of this language. We will also discuss delay issues related to these gates and ways of defining them and the way they affect timing of an entire system. Verilog has built in primitives like gates, transmission gates, and switches. These are rarely used in design (RTL Coding), but are used in post synthesis world for modeling the ASIC/FPGA cells; these cells are then used for gate level simulation, or what is called as SDF simulation. Also the output net list format from the synthesis tool, which is imported into the place and route tool, is also in Verilog gate level primitives.

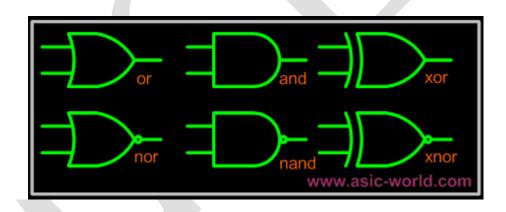

### AND& OTHERS GATE PRIMITVES:

Verilog gate level list includes standard n\_input, n\_output, and tri-state gates. Verilog instantiation of these gates are also shown in this figure. In addition, Verilog has switch level and transistor primitives that will be discussed in a later chapter. Gates categorized as n\_input gates are and, nand, or, nor, xor, and xnor. An n\_input gate has one output, which is its left-most argument, and can have any number of inputs that may be listed as its argument separated by commas. These gates can have up to two delay parameters that can appear after the name of the gate in a set of parenthesis followed by a sharp sign. An example instantiation of a 4-input nand

is shown here.

nand #(3, 5) gate1 (w, i1, i2, i3, i4);

### EXAMPLE:

Example 1: Full Adder

module FullAdder(X, Y, Cin, Cout, Sum);

input X, Y, Cin; // input terminal definitions

output Cout, Sum; // output terminal definitions

wire w1, w2, w3, w4; // internal net declarations

xor #(10) (w1, X, Y); // delay time of 10 units

xor #(10) xor2(Sum, w1, Cin); // with instance name

and #(10) (w2, X, Y);

and #(10) (w3, X, Cin);

and #(10) (w4, Y, Cin);or #(10, 8)(Cout, w2, w3, w4); // 3 input or (rise time of 10, fall // time of

8)

Endmodule

### MODULE STRUCTURES:

A module is comprised of the interface and the design behavior.

### module | macromodule identifier (port\_list) ;

ports\_declaration;

module\_body ;

### endmodule

All module declarations must begin with the **module** (or **macromodule**) keyword and end with the **endmodule** keyword. After the module declaration, an identifier is required. A ports list is an option. After that, ports declaration is given with declarations of the direction of ports and the optionally type. The body of module can be any of the following:

- Any declaration including parameter, function, task, event or any variable declaration.

- Continuous assignment.

- Gate, UDP or module instantiation.

- Specify block.

- Initial block

- Always block.

If there is no instantiation inside the module, it will be treated as a top-level module.

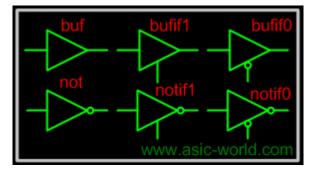

TRI STATE GATES:

Transmission gates tran and rtran are permanently on and do not have a control line. Tran can be used to interface two wires with seperate drives, and rtran can be used to weaken signals.

module transmission\_gates();

reg data\_enable\_low, in;

wire data\_bus, out1, out2;

bufif0 U1(data\_bus,in, data\_enable\_low);

buf U2(out1,in);

not U3(out2,in);

```

initial begin

```

\$monitor(

```

"@%g in=%b data_enable_low=%b out1=%b out2= b data_bus=%b",

```

\$time, in, data\_enable\_low, out1, out2, data\_bus);

data\_enable\_low = 0;

in = 0;

```

#4 data_enable_low = 1;

```

#8 \$finish;

end

```

always #2 in = \simin;

```

end

### **ARRAY OF INSTANCES OF PRIMITVES :**

Verilog uses different constructs for describing a module with different levels of detail. Verilog basic logic gates are called primitives and for describing a component using these primitives, a construct called primitive instantiation is used. See for example the multiplexer that is made of AND and OR gates. This structure can be described in Verilog as

**Basic Gates**

module MultiplexerA (input a, b, s, output w);

wire a\_sel, b\_sel, s\_bar;

not U1 (s\_bar, s);

and U2 (a\_sel, a, s\_bar);

and U3 (b\_sel, b, s);

or U4 (w, a\_sel, b\_sel);

endmodule

module MultiplexerB (input a, b, s, output w);

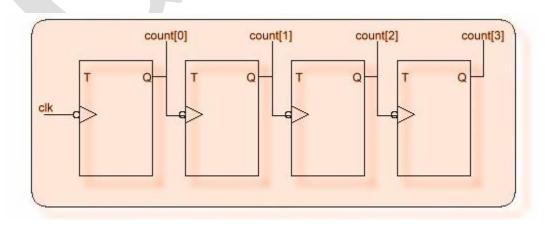

### GATE PRIMITIVES WITH FLIP FLOP:

Consider a 4-bit asynchronous counter; block diagram using flip-flops is as follows. This is a simple counter without reset or load options.

```

module counter( clk, count );

input clk;

output[3:0] count;

```

reg[3:0] count; wire clk;

```

initial

count = 4'b0;

```

```

always @( negedge clk )

count[0] <= ~count[0];

```

```

always @( negedge count[0] )

count[1] <= ~count[1];</pre>

```

```

always @( negedge count[1] )

count[2] <= ~count[2];</pre>

```

```

always @( negedge count[2] )

count[3] <= ~count[3];</pre>

```

endmodule

## **DELAYS:**

Delays specify a time in which assigned values propagate through nets or from inputs to outputs of gates.

Syntax:

#value

#(value)

#(value, value)

#(value, value, value)

Delays specify how values propagate through nets or gates.

The net delay declaration specifies a time needed to propagate values from drivers through the net. It can be used in continuous assignments (Example 1) and net declarations (Example 2).

The gate delay declaration specifies a time needed to propagate a signal change from the input of a gate input to its output. The gate delay declaration can be used in gate instantiations (Example 3).

The delays can be also used for delay control in procedural statements (Example 4 - see Procedural timing control for more explanations).

The delays declaration can contain up to three values: rise, fall, and turn-off delays. The default delay is zero. If only one delay value is specified then it is used for all signal changes. If two delays are specified then the first delay specifies the rise delay and the second delay specifies the fall delay. If the signal changes to high-impedance (z) or to unknown (x) then the smaller value will be used. This means that if delays are specified as follows: #(4,3) then the second value (3) will be used for signal changes to z or x value.

If three values are given, then the first value specifies the rise delay, the second specifies the fall delay, and the third specifies turn-off delay. If the signal changes to unknown (x) value, then the smallest of these three values will be used.

| Value changes |     | Delay used for propagation if: |                    |                    |  |

|---------------|-----|--------------------------------|--------------------|--------------------|--|

| From:         | To: | 1 delay specified              | 2 delays specified | 3 delays specified |  |

| 0             | 1   | d1                             | d1                 | d1                 |  |

| 0             | X   | d1                             | min(d1, d2)        | min(d1, d2, d3)    |  |

| 0             | Z   | d1                             | min(d1, d2)        | d3                 |  |

| 1             | 0   | d1                             | d2                 | d2                 |  |

| 1             | X   | d1                             | min(d1, d2)        | min(d1, d2, d3)    |  |

| 1             | Z   | d1                             | min(d1, d2)        | d3                 |  |

| Х             | 0   | d1                             | d2                 | d2                 |  |

| Х             | 1   | d1                             | d1                 | d1                 |  |

| Х             | Z   | d1                             | min(d1, d2)        | d3                 |  |

| Z             | 0   | d1                             | d2                 | d2                 |  |

| Z             | 1   | d1                             | d1                 | d1                 |  |

| Z             | X   | D1                             | min(d1, d2)        | min(d1, d2, d3)    |  |

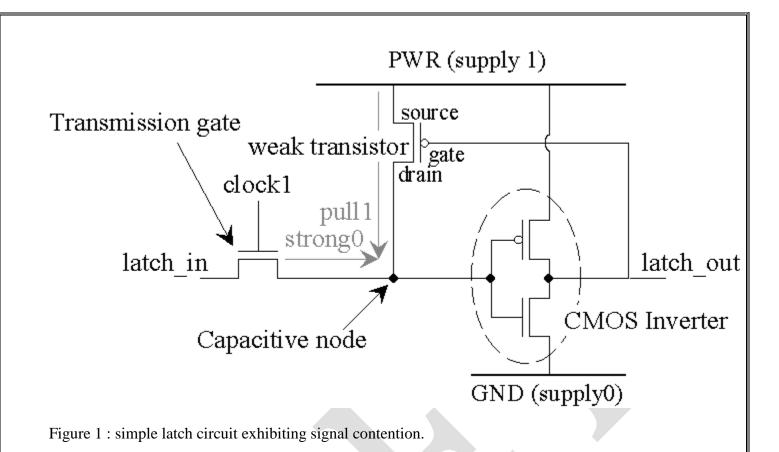

## STRENGTHS AND CONTENT RESOLUTION:

Strengths can be used to resolve which value should appear on a net or gate output.

There are two types of strengths: drive strengths (*Example 1*) and charge strengths (*Example 2*). The drive strengths can be used for nets (except **trireg** net), gates, and UDPs. The charge strengths can be

used only for **trireg** nets. The drive strength types are **supply**, **strong**, **pull**, **weak**, and **highz** strengths. The charge strength types are **large**, **medium** and **small**strengths.

All strengths can be ordered by their value. The **supply** strength is the strongest and the **highz** strength is the weakest strength level. Strength value can be displayed by system tasks (**\$display**, **\$monitor** - by using of the %v characters - see Display tasks for more explanation).

| Strength | Value | Value displayed by display tasks |

|----------|-------|----------------------------------|

| supply   | 7     | Su                               |

| strong   | 6     | St                               |

| pull     | 5     | Pu                               |

| large    | 4     | La                               |

| weak     | 3     | We                               |

| medium   | 2     | Ме                               |

| small    | 1     | Sm                               |

| highz    | 0     | HiZ                              |

## **NET TYPES:**

Nets are data types that can be used to model physical connections.

#### Net declaration:

wire range delays list\_of\_identifiers;

wand range delays list\_of\_identifiers;

wor range delays list\_of\_identifiers;

tri range delays list\_of\_identifiers;

triand range delays list\_of\_identifiers;

trior range delays list\_of\_identifiers;

tri0 range delays list\_of\_identifiers;

tri1 range delays list\_of\_identifiers;

supply0 range delays list\_of\_identifiers;

supply1 range delays list\_of\_identifiers;

trireg strength range delays list\_of\_identifiers;

#### Net declaration assignment:

**wire** strength range delays list\_of\_identifiers = expression;

wand strength range delays list\_of\_identifiers = expression;

**wor** strength range delays list\_of\_identifiers = expression;

tri strength range delays list\_of\_identifiers = expression;

**triand** strength range delays list\_of\_identifiers = expression;

**trior** strength range delays list\_of\_identifiers = expression;

**tri0** strength range delays list\_of\_identifiers = expression;

**tri1** strength range delays list\_of\_identifiers = expression;

supply0 strength range delays list\_of\_identifiers = expression;

supply1 strength range delays list\_of\_identifiers = expression;

**trireg** strength range delays list\_of\_identifiers = expression;

Net data types are used to model physical connections. They do not store values (there is only one exception - **trireg**, which stores a previously assigned value). The net data types have the value of their drivers. If a net variable has no driver, then it has a high-impedance value (z).

Nets can be declared in a net declaration statement or in a net declaration assignment

Net declarations can contain strength declarations, which specifies the strength of the logic values driven by the net (see Strengths for more details). The range declaration is used to specify multi-bit nets (vectors). The delays are used to specify propagation delays through the nets. The strength, delay and range declarations are optional

wire [7:0] a; tri tristate\_buffer; wand #5 sig\_1; trireg (small) t;

The 'a' variable is a 8-bit **wire** net.

The 'tristate\_buffer' is 1-bit tri net type variable.

The 'sig\_1' variable is 1-bit wand net type variable, which propagates driven value to its output in 5 time units.

The 't' variable is **trireg** net variable with small charge strength.

#### EXAMPLE OF BASIC DESIGN

module example();