# Digital Design Through Verilog Hdl

# **IV-YEAR II-SEM**

Dept. of Electronics and Communication Engineering

# LIST OF CONTENTS

| Sl. No. | CONTENT                                           |  |  |  |

|---------|---------------------------------------------------|--|--|--|

| 1       | Cover Page                                        |  |  |  |

| 2       | Syllabus copy                                     |  |  |  |

| 3       | Vision of the Department                          |  |  |  |

| 4       | Mission of the Department                         |  |  |  |

| 5       | PEOs and POs                                      |  |  |  |

| 6       | Course objectives and outcomes                    |  |  |  |

| 7       | Brief notes on importance of Course               |  |  |  |

| 8       | Prerequisites if any                              |  |  |  |

| 9       | Instructional Learning Outcomes                   |  |  |  |

| 10      | Course mapping with PEOs and POs                  |  |  |  |

| 11      | Class Time Table                                  |  |  |  |

| 12      | Individual Time Table                             |  |  |  |

| 13      | Micro Plan with dates and closure report          |  |  |  |

| 14      | Detailed notes                                    |  |  |  |

| 15      | Additional/missing topics                         |  |  |  |

|         | <sup>16</sup> University previous Question papers |  |  |  |

|         | <sup>17</sup> Question Bank                       |  |  |  |

| 18      | Assignment topics                                 |  |  |  |

| 19      | Unitwise bits                                     |  |  |  |

| 20      | Tutorial class sheets                             |  |  |  |

| 21      | Known gaps                                        |  |  |  |

| 22      | Discussion topics if any                          |  |  |  |

| 23      | References, Journals, websites and E-links        |  |  |  |

| 24      | Quality Control Sheets                            |  |  |  |

|         | a. Course end Survey                              |  |  |  |

|         | b. Teaching Evaluation                            |  |  |  |

| 25      | Student List                                      |  |  |  |

| 26      | Group-Wise students list for discussion topics    |  |  |  |

٦.

|                                                                                                                                                                                                    | E OF ENGINEERING AND<br>OLOGY  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|--|--|--|

| <b>DEPARTMENT OF</b> Electrical and Electronics Engineering                                                                                                                                        |                                |  |  |  |  |  |  |

| (Name of the Subject / Lab Course) :I<br>HDL                                                                                                                                                       | DIGITAL DESIGN THROUGH VERILOG |  |  |  |  |  |  |

| (JNTU CODE -58033)                                                                                                                                                                                 | Programme : UG                 |  |  |  |  |  |  |

| Branch: ECE                                                                                                                                                                                        | Version No : 04                |  |  |  |  |  |  |

| Year: IV-Year Updated on :26 -11-1                                                                                                                                                                 | 5                              |  |  |  |  |  |  |

| Semester: II-sem                                                                                                                                                                                   | No.of pages :186               |  |  |  |  |  |  |

| Classification status (Unrestricted / Res<br>Distribution List :<br>Prepared by : 1) Name :JUGAL KISHO<br>BHANDARI<br>2) Sign :<br>3) Design : Asst. Prof.<br>4) Date :<br>Verified by : 1) Name : |                                |  |  |  |  |  |  |

| 2) Sign :                                                                                                                                                                                          | 2) Sign :                      |  |  |  |  |  |  |

| 3) Design : 3) Design :                                                                                                                                                                            |                                |  |  |  |  |  |  |

| 4) Date : 4) Date :                                                                                                                                                                                |                                |  |  |  |  |  |  |

| Approved by : (HOD ) 1) Name : D                                                                                                                                                                   | r. P. Srihari                  |  |  |  |  |  |  |

| 2) Sign :                                                                                                                                                                                          |                                |  |  |  |  |  |  |

| 3) Date :                                                                                                                                                                                          |                                |  |  |  |  |  |  |

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD DIGITAL DESIGN THROUGH VERILOG (ELECTIVE – III)

# UNIT I

# **INTRODUCTION TO VERILOG:**

Verilog as HDL, Levels of Design Description, Concurrency, Simulationand Synthesis, Functional Verification, System Tasks, Programming Language Interface (PLI), Module, Simulation and Synthesis Tools.

# UNIT II

# LANGUAGE CONSTRUCTS AND CONVENTIONS:

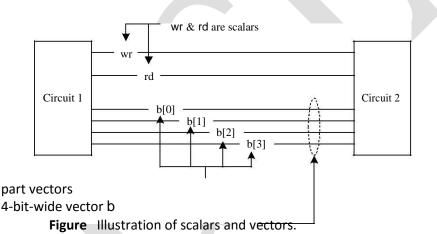

Introduction, Keywords, Identifiers, White Space Characters, Comments, Numbers, Strings, Logic Values, Strengths, Data Types, Scalars and Vectors, Parameters, Memory, Operators.

## UNIT III

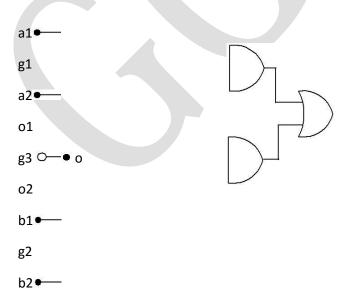

# GATE LEVEL MODELING:

Introduction, AND Gate Primitive, Module Structure, Other Gate Primitives, Illustrative Examples, Tri-State Gates, Array of Instances of Primitives, Additional Examples, Design of Flip-flopswith Gate Primitives, Delays, Strengths and Contention Resolution, Net Types, Design of BasicCircuits.

## UNIT IV

## **BEHAVIORAL MODELING:**

Introduction, Operations and Assignments, Functional Bifurcation, *Initial*Construct, *Always* Construct, Examples, Assignments with Delays, *Wait* construct, Multiple Always Blocks, Designs at Behavioral Level, Blocking and Non blocking Assignments, The *case* statement, Simulation Flow.*if* and *if-else* constructs, *assign-deassign* construct, *repeat* construct, *for* loop, the *disable* construct, *while*loop, *forever* loop, parallel blocks, *force-release* construct, Event.

## UNIT V

## MODELING AT DATA FLOW LEVEL:

Introduction, Continuous Assignment Structures, Delays and Continuous Assignments, Assignment

to Vectors, Operators.

# SWITCH LEVEL MODELING:

Basic Transistor Switches, CMOS Switch, Bi-directional Gates, Time Delays with Switch Primitives, Instantiation with 'Strengths' and 'Delays', Strength Contention with Trireg Nets.

# UNIT VI

# SYSTEM TASKS, FUNCTIONS, AND COMPILER DIRECTIVES:

Introduction, Parameters, Path Delays, Module Parameters, System Tasks and Functions, File-Based Tasks and Functions, Compiler Directives, Hierarchical Access, User- Defined Primitives (UDP).

# UNIT VII

# SEQUENTIAL CIRCUIT DESCRIPTION:

Sequential models – feedback model, capacitive model, implicit model, basic memory components, functional register, static machine coding, sequential synthesis.

## **UNIT VIII**

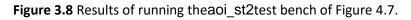

# COMPONENT TEST AND VERIFIACTION:

Test bench – combinational circuit testing, sequential circuit testing, test bench techniques, design verification, assertion verification.

## **COURSE DESCRIPTION:**

This course covers the use of Verilog and Systemverilog Languages (IEEE Std. 1800) for the design and development of digital integrated circuits, including mask-programmed integrated circuits (ASICs) and field programmable devices (FPGAs). Hierarchical top down vs. bottom up design, synthesizable vs. non-synthesizable code, design scalability and reuse, verification, hardware modeling, simulation system tasks, compiler directives and subroutines are all covered and illustrated with design examples.

3 Credits are allocated for this subject.

# **3. VISION OF THE DEPARTMENT:**

To impart quality technical education in Electronics and Communication Engineering emphasizing analysis, design/synthesis and evaluation of hardware/embedded software using various Electronic Design Automation (EDA) tools with accent on creativity, innovation and research thereby producing competent engineers who can meet global challenges with societal commitment.

# 4. MISSION OF THE DEPARTMENT:

- I. To impart quality education in fundamentals of basic sciences, mathematics, electronics and communication engineering through innovative teaching-learning processes.

- II. To facilitate Graduates define, design, and solve engineering problems in the field of Electronics and Communication Engineering using variousElectronic Design Automation (EDA) tools.

- III. To encourage research culture among faculty and students thereby facilitating them to be creative and innovative through constant interaction with R & D organizations and Industry.

- IV. To inculcate teamwork, imbibe leadership qualities, professional ethics and social responsibilities in students and faculty.

# 5. Program Educational Objectives of B. Tech (ECE) Program:

- To prepare students with excellent comprehension of basic sciences, mathematics and engineering subjects facilitating them to gain employment or pursue postgraduate studies with an appreciation for lifelong learning.

- II. To train students with problem solving capabilities such as analysis and design with adequate practical skills wherein they demonstrate creativity and innovation that would enable them to develop state of the art equipment and technologies of multidisciplinary nature for societal development.

- III. To inculcate positive attitude, professional ethics, effective communication and interpersonal skills which would facilitate them to succeed in the chosen profession

exhibiting creativity and innovation through research and development both as team member and as well as leader.

# **Program Outcomes of B.Tech ECE Program:**

- 1. An ability to apply knowledge of Mathematics, Science, and Engineering to solve complex engineering problems of Electronics and Communication Engineering systems.

- 2. An ability to model, simulate and design Electronics and Communication Engineering systems, conduct experiments, as well as analyze and interpret data and prepare a report with conclusions.

- 3. An ability to design an Electronics and Communication Engineering system, component, or process to meet desired needs within the realistic constraints such as economic, environmental, social, political, ethical, health and safety, manufacturability and sustainability.

- 4. An ability to function on multidisciplinary teams involving interpersonal skills.

- 5. An ability to identify, formulate and solve engineering problems of multidisciplinary nature.

- 6. An understanding of professional and ethical responsibilities involved in the practice of Electronics and Communication Engineering profession.

- 7. An ability to communicate effectively with a range of audience on complex engineering problems of multidisciplinary nature both in oral and written form.

- 8. The broad education necessary to understand the impact of engineering solutions in a global, economic, environmental and societal context.

- 9. Recognition of the need for, and an ability to engage in life-long learning and acquire the capability for the same.

- 10. A knowledge of contemporary issues involved in the practice of Electronics and Communication Engineering profession

- 11. An ability to use the techniques, skills and modern engineering tools necessary for engineering practice.

- 12. An ability to use modern Electronic Design Automation (EDA) tools, software and electronic equipment to analyze, synthesize and evaluate Electronics and Communication Engineering systems for multidisciplinary tasks.

- 13. Apply engineering and project management principles to one's own work and also to manage projects of multidisciplinary nature.

# 6. Course objectives and outcomes

*Course Objectives:*

- The ability to code and simulate any digital function in Verilog HDL.

- Know the difference between synthesizable and non-synthesizable code.

- Understand library modeling, behavioral code and the differences between them.

- Understand the differences between simulator algorithms.

- Learn good coding techniques per current industrial practices.

- Understand logic verification using Verilog simulation.

## *Course outcomes:*

## Subject: Digital Design through Verilog HDL

- CO 1: Students will have an ability to describe Verilog hardware description languages (HDL).

- CO 2: Students will be able to Design Digital Circuits in Verilog HDL.

- CO 3: Ability to write behavioral models of digital circuits.

- CO 4: Ability to write Register Transfer Level (RTL) models of digital circuits.

- CO 5: Ability to verify behavioral and RTL models.

- CO 6: Students will have an ability to describe standard cell libraries and FPGAs.

- CO 7: To Synthesize RTL models to standard cell libraries and FPGAs.

- CO 8: To Implement RTL models on FPGAs and Testing & Verification.

## Brief note on importance of course

This course is intended to provide a thorough coverage of Verilog HDL concepts based on fundamental principles of VLSI Design.

- 1) This is the basic fundamental subject for the programming of the digital Electronics.

- 2) This subject is required to understand the programming of the combinational and sequential circuit designs.

- 3) By studying this subject, the students can design and understand digital systems and its importance.

- 4) Large and complicated digital circuits can be incorporated into hardware by using Verilog, a hardware description language (HDL). Design through Verilog HDL affords novices the opportunity to perform all of these tasks, while also offering seasoned professionals a comprehensive resource on this dynamic tool.

- 5) Describing a design using Verilog is only half the story: writing test-benches, testing a design for all its desired functions, and how identifying and removing the faults remain significant challenges. Design Through Verilog HDL addresses each of these issues concisely and effectively.

- 6) The students logical thinking capability will be improved which will help in placements and in their future technical assignments.

# 8. Prerequisites:

- 1) Concepts of switching theory and logic design.

- 2) A basic understanding of digital hardware design and verification.

# 9. Instructional objectives and Learning outcomes:

UNIT I

# **Introduction to Verilog HDL:**

After completion of this unit, students are able to:

- 1. Students understand the importance of HDL (Hardware Descriptive Language) and apply the knowledge ofBoolean algebra to design and development digital Systems.

- 2. Understand the difference between concurrent and sequential programming.

- 3. Issues related to simulation and synthesis models.

# UNIT II

## Language Constructs and Conventions:

After completion of this unit, students are able to:

- 1. Knowledge of language constructs

- 2. Pertaining to Semantic and syntactical errors in programming using HDL

3. Limitation of HDL

# UNIT III

# **Gate Level Modeling:**

After completion of this unit, students are able to:

- 1. Student will learn conventional structural modeling of digital systems.

- 2. Learn to model language defined primitive gates

- 3. Understand importance of component structure in Verilog.

- 4. Learn Hierarchical digital system building

# UNIT IV

# Modeling at Dataflow Level:

After completion of this unit, students are able to:

1. Continuous assignment operator based model construction will be learnt.

# UNIT V

After completion of this unit, students are able to:

# **Behavioral Modeling:**

- 1. Students will be familiarized to high level abstraction of digital systems with behavioral modeling of systems.

- 2. RTL modeling of digital systems

- 3. Will be made familiar to behavioral constructs like 'always' ,'initial','if', 'ifelse','case'..etc

- 4. Register and array modeling.

# Switch Level Modeling:

- 5. Students will learn low-level abstraction of digital systems.

- 6. Switch level primitives will be learnt

- 7. Made to familiarize to different strengths of logic values

# UNIT VI

# System Tasks, Functions and Compiler Directives:

After completion of this unit, students are able to:

- 1. Understand the importance of system tasks and functions

- 2. Understand compiler directives.

- 3. Understand user defined primitives and learn to model systems using UDP

- 4. Learn the intricacies associated with usage of functions and tasks in packages

- 5. Learn package declaration and package usage in project building

# UNIT VII

## **Sequential Circuit Description:**

After completion of this unit, students are able to:

- 1. Learn to model Sequential circuits at higher level of abstraction using RTL modeling

- 2. Will be able to design static and dynamic memories

- 3. Will learn to model in behavioral style of binary encoding and one hot encoding

# UNIT VIII

# **Component Test and Verification:**

After completion of this unit, students are able to:

- 1. Students understand Test bench generation

- 2. Producing of test vectors to test the digital systems at higher level of abstraction.

# **10.** Mapping of Course outcomes with Programme outcomes:

\*When the course outcome weightage is < 40%, it will be given as moderately correlated (1). \*When the course outcome weightage is >40%, it will be given as strongly correlated (2).

| POs                                                                                                  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 |

|------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|

| Digital Design<br>Through Verilog<br>HDL                                                             | 2 | 2 | 2 | 2 | 2 | 1 |   | 1 | 2 | 2  | 2  |    | 1  |

| <b>CO 1:</b> Students will be able to describe Verilog hardware description languages (HDL).         | 2 | 2 | 2 | 2 | 2 | 1 |   |   | 2 | 2  | 2  |    | 1  |

| <b>CO 2</b> :Students will be<br>able to Design<br>Digital Circuits in<br>Verilog HDL.               | 2 | 2 | 2 | 2 | 2 |   |   |   | 2 | 2  | 1  |    |    |

| <b>CO3</b> :Ability to write behavioral models of digital circuits.                                  | 1 | 1 |   | 2 |   |   |   | 1 | 2 | 1  | 1  |    |    |

| <b>CO4:</b> Ability to write<br>Register Transfer<br>Level (RTL) models<br>of digital circuits.      | 1 | 2 | 2 |   | 2 |   |   | 1 | 2 | 1  | 1  |    |    |

| <b>CO5</b> :Ability to verify behavioral and RTL models.                                             | 2 | 2 | 2 | 2 | 2 |   |   |   | 2 | 1  | 1  |    |    |

| <b>CO 6:</b> Students will<br>have an abilityto<br>describe standard<br>cell libraries and<br>FPGAs. | 2 | 2 | 2 |   | 2 |   |   |   | 2 | 1  | 1  |    |    |

| <b>CO 7:</b> To Synthesize<br>RTL models to<br>standard cell<br>libraries and FPGAs.                 | 1 | 2 | 2 |   | 2 |   |   |   |   | 1  | 1  |    |    |

| <b>CO 8:</b> To Implement<br>RTL models on<br>FPGAs and Testing<br>& Verification.                   | 1 | 2 | 2 |   | 2 |   |   | 1 | 2 | 1  | 2  |    | 1  |

11. Class Time Table:

# **12.** Individual Time Table:

# 13. Micro Plan With Dates & Closure Report:

| SL.<br>NO | Unit<br>No. | Total<br>no. of<br>peroi<br>ds | Date     | Topics to be covered in one<br>lecture                                                                           | Regula<br>r/<br>Additio<br>nal | Teaching<br>aids used<br>LCD/<br>OHP/<br>BB | Remarks |

|-----------|-------------|--------------------------------|----------|------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------|---------|

| 1         | I           | 4                              | 11/12/15 | Verilog as HDL, Levels of Design<br>Description, Concurrency, Verilog<br>as HDL, Levels of Design<br>Description | Regular                        | OHP,BB                                      |         |

| 2         |             |                                | 11/12/15 | Concurrency Simulation and<br>Synthesis, Functional Verification,<br>System Tasks                                | Regular                        | OHP,BB                                      |         |

| 3         |             |                                | 12/12/15 | Programming Language Interface<br>(PLI), Module, Simulation and<br>Synthesis Tools                               | Regular                        | OHP,BB                                      |         |

| 4         |             |                                | 12/12/15 | Tutorial class-1                                                                                                 |                                |                                             |         |

IV B.Tech II-Sem

| 5  | II  | 3 | 18/12/15 | LANGUAGE CONSTRUCTS<br>AND<br>CONVENTIONS:Introduction,<br>KeywordsIdentifiers, White Space<br>Characters, Comments, Numbers,<br>Strings, Logic Values, Strengths | Regular        | BB     |

|----|-----|---|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|

| 6  |     |   | 18/12/15 | Data Types, Scalars and Vectors,<br>Parameters, Memory, Operators,<br>System Tasks, Exercises.                                                                    | Regular        | OHP,BB |

| 7  |     |   | 19/12/15 | Tutorial class-2                                                                                                                                                  |                | BB     |

| 8  | III | 4 | 26/12/15 | GATE LEVEL MODELING:<br>Introduction, AND Gate Primitive,<br>Module Structure                                                                                     | Regular        | OHP,BB |

| 9  |     |   | 26/12/15 | Other Gate Primitives, Illustrative<br>Examples, Tri-State Gates                                                                                                  | Regular        | OHP,BB |

| 10 |     |   | 02/01/16 | Array of Instances of Primitives,<br>Additional Examples                                                                                                          | Regular        | OHP,BB |

| 11 |     |   | 02/01/16 | Design of Flip-flops with Gate<br>Primitives, Delays                                                                                                              | Regular        | BB     |

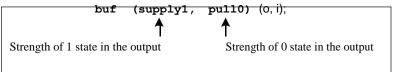

| 12 |     |   | 08/01/16 | StrengthsandContentionResolution,NetTypes,Design ofBasic Circuits.Image: Circuits.Image: Circuits.Image: Circuits.                                                | Regular        | BB     |

| 13 |     |   | 08/01/16 | Verilog designs for various rounding methods                                                                                                                      | Additio<br>nal | OHP,BB |

| 14 |     |   | 08/01/16 | Tutorial class-3                                                                                                                                                  |                |        |

| 15 | IV  | 4 | 22/01/16 | BEHAVIORAL MODELING:<br>Introduction, Operations and<br>Assignments, Functional<br>Bifurcation, <i>Initial</i> Construct,<br><i>Always</i> Construct, Examples    | Regular        | OHP,BB |

| 16 |     |   | 22/01/16 | Assignments with Delays, <i>Wait</i><br>construct, Multiple Always Blocks,<br>Designs at Behavioral Level                                                         | Regular        | OHP,BB |

| 17 |     |   | 29/01/16 | Blocking and Non blocking<br>Assignments, The <i>case</i> statement,<br>Simulation Flow. <i>if</i> and <i>if-else</i><br>constructs                               |                | BB     |

IV B.Tech II-Sem

| 18 |    |   | 29/01/16 | Assign-de-assign construct, repeat<br>construct, for loop, the disable<br>construct,while loop, forever loop,<br>parallel blocks, force-release<br>construct, Event. |                | BB     |

|----|----|---|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|

| 19 |    |   | 05/02/16 | Tutorial class-4                                                                                                                                                     |                | BB     |

| 20 |    |   | 05/02/16 | Solving university papers                                                                                                                                            |                |        |

| 21 |    |   | 06/02/16 | Assignment test-1                                                                                                                                                    |                |        |

| 22 |    |   |          | Mid test-1                                                                                                                                                           |                |        |

| 23 | V  | 6 | 13/02/16 | MODELING AT DATAFLOW<br>LEVEL: Introduction, Continuous<br>Assignment Structures, Delays and<br>Continuous Assignments                                               | Regular        | OHP,BB |

| 24 |    |   | 13/02/16 | Assignment to Vectors, Operators.                                                                                                                                    | Regular        | OHP,BB |

| 25 |    |   | 19/02/16 | SWITCH LEVEL MODELING:<br>Introduction Basic Transistor<br>Switches, CMOS Switch, Bi-<br>directional Gates                                                           | Regular        | OHP,BB |

| 26 |    |   | 19/02/16 | Time Delays with Switch<br>Primitives, Instantiations with<br>Strengths and Delays                                                                                   | Regular        | OHP,BB |

| 27 |    |   | 20/02/16 | Strength Contention with Trireg<br>Nets.                                                                                                                             | Regular        | BB     |

| 28 |    |   | 20/02/16 | Combinational synthesis                                                                                                                                              | Additio<br>nal | BB     |

| 29 | VI | 4 | 26/02/16 | Introduction, Parameters, Path<br>Delays, Module Parameters,<br>System Tasks and Functions                                                                           | Regular        | OHP,BB |

| 30 |    |   | 26/02/16 | File-Based Tasks and Functions,<br>Compiler Directives, Hierarchical<br>Access,                                                                                      | Regular        | OHP,BB |

| 31 |    |   | 27/02/16 | User- Defined Primitives (UDP)                                                                                                                                       | Regular        | OHP,BB |

IV B.Tech II-Sem

| 32 |      |   | 27/02/16 | Tutorial class- 5 & 6                                                             |         | BB     |

|----|------|---|----------|-----------------------------------------------------------------------------------|---------|--------|

| 33 | VII  | 4 | 04/03/16 | Sequential Models – FeedBack<br>Model, Capacaitive Model, Implicit<br>Model       | Regular | OHP,BB |

| 34 |      |   | 04/03/16 | Basic Memory Components,<br>Functional Register                                   | Regular | OHP,BB |

| 35 |      |   | 05/03/16 | Static Machine Coding                                                             | Regular | OHP,BB |

| 36 |      |   | 05/03/16 | Sequential Synthesis                                                              | Regular | OHP,BB |

| 37 |      |   | 11/03/16 | Tutorial class – 7                                                                |         | BB     |

| 38 | VIII | 4 | 12/03/16 | Component Test and Verification:<br>Test Bench – Combinational<br>Circuit Testing | Regular | OHP,BB |

| 39 |      |   | 18/03/16 | Test Bench – Sequential Circuit<br>Testing                                        | Regular | OHP,BB |

| 40 |      |   | 19/03/16 | Test Bench Techniques                                                             | Regular | OHP,BB |

| 41 |      |   | 26/03/16 | Design Verification                                                               | Regular | OHP,BB |

| 42 |      |   | 01/04/16 | Assertion Verification                                                            | Regular | OHP,BB |

| 43 |      |   | 01/04/16 | Tutorial Class – 8                                                                |         | BB     |

| 44 |      |   | 02/04/16 | Solving university papers                                                         |         | BB     |

| 45 |      |   | 09/04/16 | Assignment test-2                                                                 |         |        |

| 46 |      |   |          | Mid test-2                                                                        |         |        |

Course closer Report on Digital Design Through Verilog HDL:

| 1. | No. of classes Planned to complete the course      | : | 36    |

|----|----------------------------------------------------|---|-------|

| 2. | No.of classes conducted                            | : | ECE-A |

|    |                                                    |   | ECE-B |

|    |                                                    |   | ECE-C |

| 3. | No. of students appeared the External Examination  | : | ECE-A |

|    |                                                    |   | ECE-B |

|    |                                                    |   | ECE-C |

| 4. | No. of students passed in the External Examination | : | ECE-A |

|    |                                                    |   | ECE-B |

|    |                                                    |   | ECE-C |

| 5. | No. of Students failed in the External Examination | : | ECE-A |

|    |                                                    |   | ECE-B |

|    |                                                    |   | ECE-C |

| 6. | Pass percentage of each section                    | : | ECE-A |

|    |                                                    |   | ECE-B |

|    |                                                    |   | ECE-C |

| 7. | Maximum marks obtained in the Course               | : | ECE-A |

|    |                                                    |   | ECE-B |

|    |                                                    |   | ECE-C |

|    |                                                    |   |       |

# **14.** Detailed Notes:

1

# INTRODUCTION TO VLSI DESIGN

#### 1.1 INTRODUCTION

The word digital has made a dramatic impact on our society. More significant is a continuous trend towards digital solutions in all areas – from electronic instrumentation, control, data manipulation, signals processing, telecom-munications *etc.*, to consumer electronics. Development of such solutions has been possible due to good digital system design and modeling techniques.

#### 1.2 CONVENTIONAL APPROACH TO DIGITAL DESIGN

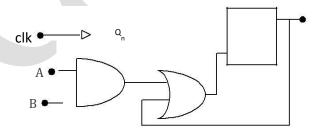

Digital ICs of SSI and MSI types have become universally standardized and have beenaccepted for use. Whenever a designer has to realize a digital function, he uses a standard set of ICs along with a minimal set of additional discrete circuitry. Consider a simple example of realizing a function as  $Q_{n+1} = Q_n + (A B)$

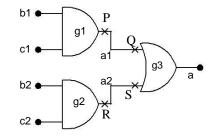

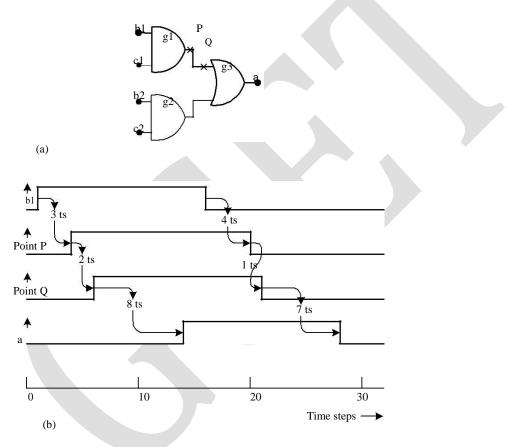

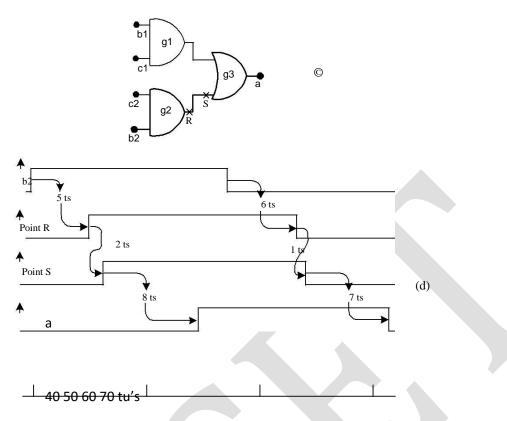

Here  $Q_{n,A}$ , and *B* are Boolean variables, with  $Q_n$  being the value of *Q* at the *n*th time step. Here *A B* signifies the logical AND of *A* and *B*; the '+' symbol signifies the logical OR of the logic variables on either side. A circuit to realize the function is shown in Figure 1.1. The circuit can be realized in terms of two ICs – an A-O-I gate and a flip-flop. It can be directly wired up, tested, and used.

Figure 1.1 A simple digital circuit.

With comparatively larger circuits, the task mostly reduces to one of identifying the set of ICs necessary for the job and interconnecting; rarely does one have to resort to a microlevel design [Wakerly]. The accepted approach to digital design here is a mix of the top-down and bottom-up approaches as follows [Hill & Peterson]:

Decide the requirements at the system level and translate them to circuit requirements.

Identify the major functional blocks required like timer, DMA unit, registerfile *etc.*, say as in the design of a processor. Whenever a function can be realized using a standard IC, use the same –for example programmable counter, mux, demux, *etc*.

Whenever the above is not possible, form the circuit to carry out the block functions using standard SSI – for example gates, flip-flops, *etc*.

Use additional components like transistor, diode, resistor, capacitor, etc., wherever essential.

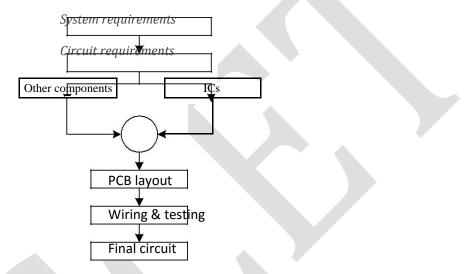

Once the above steps are gone through, a paper design is ready. Starting with the paper design, one has to do a circuit layout. The physical location of all the components is tentatively decided; they are interconnected and the 'circuit-on-paper' is made ready. Once a paper design is done, a layout is carried out and a net-list prepared. Based on this, the PCB is fabricated, and populated and all the populated cards tested and debugged. The procedure is shown as a process flowchart in Figure 1.2.

Figure 1.2 Sequence of steps in conventional electronic circuit design.

At the debugging stage one may encounter three types of problems: *Functional mismatch*: The realized and expected functions are different. Onemay have to go through the relevant functional block carefully and locate any error logically. Finally the necessary correction has to be carried out in

hardware.

*Timing mismatch*: The problem can manifest in different forms. Onepossibility is due to the signal going through different propagation delays in two paths and arriving at a point with a timing mismatch. This can cause faulty operation. Another possibility is a race condition in a circuit involving asynchronous feedback. This kind of problem may call for elaborate debugging. The preferred practice is to do debugging at smaller module stages and ensuring that feedback through larger loops is avoided: It becomes

essential to check for the existence of long asynchronous loops.

*Overload*: Some signals may be overloaded to such an extent that the signaltransition may be unduly delayed or even suppressed. The problem manifests as reflections and erratic behavior in some cases (The signal has to be suitably buffered here.). In fact, overload on a signal can lead to timing mismatches.

The above have to be carried out after completion of the prototype PCB manufacturing; it involves cost, time, and also a redesigning process to develop a bugfree design.

1.3 VLSI DESIGN

The complexity of VLSIs being designed and used today makes the manual approach to design impractical. Design automation is the order of the day. With the rapid technological developments in the last two decades, the status of VLSI technology is characterized by the following [Wai-kai, Gopalan]: A steady increase in the size and hence the functionality of the ICs.

A steady reduction in feature size and hence increase in the speed of operation as well as gate or transistor density.

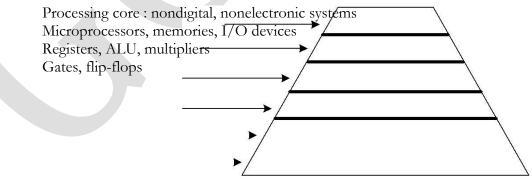

> A steady improvement in the predictability of circuit behavior. A steady increase in the variety and size of software tools for VLSI design. The above developments have resulted in a proliferation of approaches to VLSI design. We briefly describe the procedure of automated design flow [Rabaey, Smith MJ]. The aim is more to bring out the role of a Hardware Description Language (HDL) in the design process. An abstraction based model is the basis of the automated design.

#### Abstraction Model

The model divides the whole design cycle into various domains (see Figure 1.3). With such an abstraction through a division process the design is carried out in different layers. The designer at one layer can function without bothering about the layers above or below. The thick horizontal lines separating the layers in the figure signify the compartmentalization. As an example, let us consider design at the gate level. The circuit to be designed would be described in terms of truth tables and state tables. With these as available inputs, he has to express them as Boolean logic equations and realize them in terms of gates and flip-flops. In turn, these form the inputs to the layer immediately below. Compartmentalization of the approach to design in the manner described here is the essence of abstraction; it is the basis for development and use of CAD

tools in VLSI design at various levels.

The design methods at different levels use the respective aids such as Boolean equations, truth tables, state transition table, *etc*. But the aids play only a small role in the process. To complete a design, one may have to switch from one tool to another, raising the issues of tool compatibility and learning new environments.

#### 1.4 ASIC DESIGN FLOW

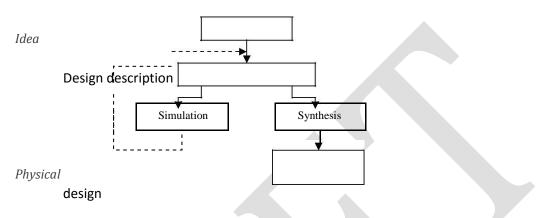

As with any other technical activity, development of an ASIC starts with an idea and takes tangible shape through the stages of development as shown in Figure 1.4 and shown in detail in Figure 1.5. The first step in the process is to expand the idea in terms of behavior of the target circuit. Through stages of programming, the same is fully developed into a design description – in terms of well defined standard constructs and conventions.

#### Structural domain

Sem

Transistors, L, R, C \_\_\_\_\_ Circuit (differential equations)

Silicon (none)

Figure 1.3 Design domain and levels of abstraction.

Geometric objects -

Figure 1.4 Major activities in ASIC design.

The design is tested through a simulation process; it is to check, verify, and ensure that what is wanted is what is described. Simulation is carried out through dedicated tools. With every simulation run, the simulation results are studied to identify errors in the design description. The errors are corrected and another simulation run carried out. Simulation and changes to design description together form a cyclic iterative process, repeated until an error-free design is evolved.

Design description is an activity independent of the target technology or manufacturer. It results in a description of the digital circuit. To translate it into a tangible circuit, one goes through the physical design process. The same constitutes a set of activities closely linked to the manufacturer and the target technology

## 1.4.1 Design Description

The design is carried out in stages. The process of transforming the idea into a detailed circuit description in terms of the elementary circuit components constitutes design description. The final circuit of such an IC can have up to a billion such components; it is arrived at in a step-by-step manner.

The first step in evolving the design description is to describe the circuit in terms of its behavior. The description looks like a program in a high level language like C. Once the behavioral level design description is ready, it is tested extensively with the help of a simulation tool; it checks and confirms that all the expected functions are carried out satisfactorily. If necessary, this behavioral level routine is edited, modified, and rerun – all done manually. Finally, one has a design for the expected system – described at the behavioral level. The behavioral design forms the input to the synthesis tools, for circuit synthesis. The behavioral constructs not supported by the synthesis tools are replaced by data flow and gate level constructs. To surmise, the designer has to develop synthesizable codes for his design.

The design at the behavioral level is to be elaborated in terms of known and acknowledged functional blocks. It forms the next detailed level of design description. Once again the design is to be tested through simulation and iteratively corrected for errors. The elaboration can be continued one or two steps further. It leads to a detailed design description in terms of logic gates and transistor switches.

## 1.4.2 Optimization

The circuit at the gate level – in terms of the gates and flip-flops – can be redundant in nature. The same can be minimized with the help of minimization tools. The step is not shown separately in the figure. The minimized logical design is converted to a circuit in terms of the switch level cells from

standard libraries provided by the foundries. The cell based design generated by the tool is the last step in the logical design process; it forms the input to the first level of physical design [Micheli].

DIGITAL DESIGN THROUGH VERILOG HDL

#### 1.4.3 Simulation

The design descriptions are tested for their functionality at every level – behavioral, data flow, and gate. One has to check here whether all the functions are carried out as expected and rectify them. All such activities are carried out by the simulation tool. The tool also has an editor to carry out any corrections to the source code. Simulation involves testing the design for all its functions, functional sequences, timing constraints, and specifications. Normally testing and simulation at all the levels – behavioral to switch level – are carried out by a single tool; the same is identified as "scope of simulation tool" in Figure 1.5. Synthesis

With the availability of design at the gate (switch) level, the logical design is complete. The corresponding circuit hardware realization is carried out by a synthesis tool. Two common approaches are as follows:

The circuit is realized through an FPGA [Oldfield]. The gate level design description is the starting point for the synthesis here. The FPGA vendors provide an interface to the synthesis tool. Through the interface the gate level design is realized as a final circuit. With many synthesis tools, one can directly use the design description at the data flow level itself to realize the final circuit through an FPGA. The FPGA route is attractive for limited

volume production or a fast development cycle.

The circuit is realized as an ASIC. A typical ASIC vendor will have his own library of basic components like elementary gates and flip-flops. Eventually the circuit is to be realized by selecting such components and interconnecting them conforming to the required design. This constitutes the physical design. Being an elaborate and costly process, a physical design may call for an intermediate functional verification through the FPGA route. The circuit realized through the FPGA is tested as a prototype. It provides another opportunity for testing the design closer to the final circuit.

## 1.4.5 Physical Design

A fully tested and error-free design at the switch level can be the starting point for a physical design [Baker & Boyce, Wolf]. It is to be realized as the final circuit using (typically) a million components in the foundry's library. The step-by-step activities in the process are described briefly as follows:

*System partitioning*: The design is partitioned into convenient compartmentsor functional blocks. Often it would have been done at an earlier stage itself and the software design prepared in terms of such blocks. Interconnection of

the blocks is part of the partition process.

*Floor planning*: The positions of the partitioned blocks are planned and theblocks are arranged accordingly. The procedure is analogous to the planning and arrangement of domestic furniture in a residence. Blocks with I/O pins are kept close to the periphery; those which interact frequently or through a large number of interconnections are kept close together, and so on. Partitioning and floor planning may have to be carried out and refined

iteratively to yield best results.

*Placement*: The selected components from the ASIC library are placed in position on the "Silicon floor." It is done with each of the blocks above.

*Routing*: The components placed as described above are to be interconnected to the rest of the block: It is done with each of the blocks by suitably routing the interconnects. Once the routing is complete, the physical design cam is taken as complete. The final mask for the design can be made at this stage and the ASIC manufactured in the foundry.

## 1.4.6 Post Layout Simulation

Once the placement and routing are completed, the performance specifications like silicon area, power consumed, path delays, *etc.*, can be computed. Equivalent circuit can be extracted at the component level and performance analysis carried out. This constitutes the final stage called "verification." One may have to go through the placement and routing activity once again to improve performance.

# 1.4.7 Critical Subsystems

The design may have critical subsystems. Their performance may be crucial to the overall performance; in other words, to improve the system performance substantially, one may have to design such subsystems afresh. The design here may imply redefinition of the basic feature size of the component, component design, placement of components, or routing done separately and specifically for the subsystem. A set of masks used in the foundry may have to be done afresh for the purpose.

1.5 ROLE OF HDL

An HDL provides the framework for the complete logical design of the ASIC. All the activities coming under the purview of an HDL are shown enclosed in bold dotted lines in Figure 1.4. Verilog and VHDL are the two most commonly used HDLs today. Both have constructs with which the design can be fully described at all the levels. There are additional constructs available to facilitate setting up of the test bench, spelling out test vectors for them and "observing" the outputs from the designed unit.

IEEE has brought out Standards for the HDLs, and the software tools conform to them. Verilog as an HDL was introduced by Cadence Design Systems; they placed it into the public domain in 1990. It was established as a formal IEEE Standard in 1995. The revised version has been brought out in 2001. However, most of the simulation tools available today conform only to the 1995 version of the standard. Verilog HDL used by a substantial number of the VLSI designers today is the topic of discussion of the book.

1.6 VERILOG AS AN HDL

Verilog has a variety of constructs as part of it. All are aimed at providing a functionally tested and a verified design description for the target FPGA or ASIC. The language has a dual function – one fulfilling the need for a design description and the other fulfilling the need for verifying the design for functionality and timing constraints like propagation delay, critical path delay, slack, setup, and hold times [Smith DJ, Wai-Kai].

Verilog as an HDL has been introduced here and its overall structure explained. A widely used development tool for simulation and synthesis has been introduced; the brief procedural explanation provided suffices to try out the Examples and Exercises in the text.

#### 1.7 LEVELS OF DESIGN DESCRIPTION

The components of the target design can be described at different levels with the help of the constructs in Verilog.

## 1.7.1 Circuit Level

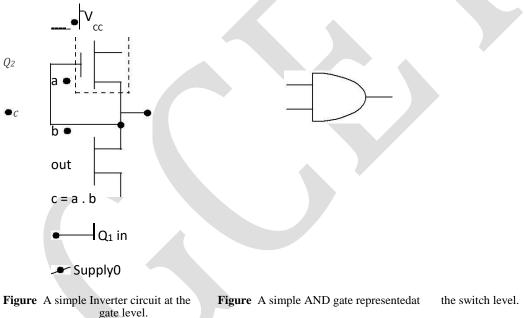

At the circuit level, a switch is the basic element with which digital circuits are built. Switches can be combined to form inverters and other gates at the next higher level of abstraction. Verilog has the basic MOS switches built into its constructs, which can be used to build basic circuits like inverters, basic logic gates, simple 1-bit dynamic and static memories. They can be used to build up larger designs to simulate at the circuit level, to design performance critical circuits. Figure 2.1 shows the circuit of an inverter suitable for description with the switch level constructs of Verilog.

## 1.7.2 Gate Level

At the next higher level of abstraction, design is carried out in terms of basic gates. All the basic gates are available as ready modules called "Primitives." Each such primitive is defined in terms of its inputs and outputs. Primitives can be incorporated into design descriptions directly. Just as full physical hardware can be built using gates, the primitives can be used repeatedly and judiciously to build larger systems. Figure 2.2 shows an AND gate suitable for description using the

Department of ECE

gate primitive of Verilog. The gate level modeling or structural modeling as it is sometimes called is akin to building a digital circuit on a bread board, or on a PCB. One should know the structure of the design to build the model here. One can also build hierarchical circuits at this level. However, beyond 20 to 30 of such gate primitives in a circuit, the design description becomes unwieldy; testing and debugging become laborious.

#### 1.7.3 Data Flow

Data flow is the next higher level of abstraction. All possible operations on signals and variables are represented here in terms of assignments. All logic and algebraic operations are accommodated. The assignments define the continuous functioning of the concerned block. At the data flow level, signals are assigned through the data manipulating equations. All such assignments are concurrent in nature. The design descriptions are more compact than those at the gate level. Figure 2.3 shows an A-O-I relationship suitable for description with the Verilog constructs at the data flow level.

<sup>1.7.4</sup> Behavioral Level

Behavioral level constitutes the highest level of design description; it is essentially at the system level itself [Bhaskar]. With the assignment possibilities, looping constructs and conditional branching possible, the design description essentially looks like a "C" program. The statements involved are "dense" in function. Compactness and the comprehensive nature of the design description make the development process fast and efficient. Figure 2.4 shows an A-O-I gate expressed in pseudo code suitable for description with the behavioral level constructs of Sem

#### Verilog. 1.7.5 The Overall Design Structure in Verilog

The possibilities of design description statements and assignments at different levels necessitate their accommodation in a mixed mode. In fact the design statements coexisting in a seamless manner within a design module is a significant characteristic of Verilog. Thus Verilog facilitates the mixing of the abovementioned levels of design. A design built at data flow level can be instantiated to form a structural mode design. Data flow assignments can be incorporated in designs which are basically at behavioral level.

# 1.8 CONCURRENCY

In an electronic circuit all the units are to be active and functioning concurrently. The voltages and currents in the different elements in the circuit can change simultaneously. In turn the logic levels too can change. Simulation of such a circuit in an HDL calls for concurrency of operation. A number of activities – may be spread over different modules – are to be run concurrently here. Verilog simulators are built to simulate concurrency. (This is in contrast to programs in the normal languages like C where execution is sequential.) Concurrency is achieved by proceeding with simulation in equal time steps. The time step is kept small enough to be negligible compared with the propagation delay values. All the activities scheduled at one time step are completed and then the simulator

| e a.b c.d | If $(a, b, c \text{ or } d \text{ changes})$<br>Compute $e$ as<br>$e  \overline{a.b \ c.d}$ |

|-----------|---------------------------------------------------------------------------------------------|

|-----------|---------------------------------------------------------------------------------------------|

**Figure** An A-O-I gate represented as a **Figure** An A-O-I gate in pseudo code at data flow type of relationship. advances to the next time step and so on. The time step values refer to simulation time and not real time. One can redefine timescales to suit technology as and when necessary and carry out test runs.

In some cases the circuit itself may demand sequential operation as with data transfer and memory-based operations. Only in such cases sequential operation is ensured by the appropriate usage of sequential constructs from Verilog HDL.

# 1.9 SIMULATION AND SYNTHESIS

The design that is specified and entered as described earlier is simulated for functionality and fully debugged. Translation of the debugged design into the corresponding hardware circuit (using an FPGA or an ASIC) is called "synthesis." The tools available for synthesis relate more easily with the gate level and data flow level modules [Smith MJ]. The circuits realized from them

are essentially direct translations of functions into circuit elements. In contrast many of the behavioral level constructs are not directly synthesizable; even if synthesized they are likely to yield relatively redundant or wrong hardware. The way out is to take the behavioral level modules and redo each of them at lower levels. The process is carried out successively with each of the behavioral level modules until practically the full design is available as a pack of modules at gate and data flow levels (more commonly called the "RTL level").

## 1.10 FUNCTIONAL VERIFICATION

Testing is an essential ingredient of the VLSI design process as with any hardware circuit. It has two dimensions to it – functional tests and timing tests. Both can be carried out with Verilog. Often testing or functional verification is carried out by setting up a "test bench" for the design. The test bench will have the design instantiated in it; it will generate necessary test signals and apply them to the instantiated design. The outputs from the design are brought back to the test bench for further analysis. The input signal combinations, waveforms and sequences required for testing are all to be decided in advance and the test bench configured based on the same.

The test benches are mostly done at the behavioral level. The constructs there are flexible enough to allow all types of test signals to be generated.

In the process of testing a module, one may have to access variables buried inside other modules instantiated within the master module. Such variables can be accessed through suitable hierarchical addressing.

## Test Inputs for Test Benches

Any digital system has to carry out a number of activities in a defined manner. Once a proper design is done, it has to be tested for all its functional aspects. The system has to carry out all the expected activities and not falter. Further, it should not malfunction under any set of input conditions. Functional testing is carried out to check for such requirements. Test inputs can be purely combinational, periodic, numeric sequences, random inputs, conditional inputs, or combinations of these. With such requirements, definition and design of test benches is often as challenging as the design itself.

As the circuit design proceeds, one develops smaller blocks and groups them together to form bigger circuit units. The process is repeated until the whole system is fully built up. Every stage calls for tests to see whether the subsystem at that layer behaves in the manner expected. Such testing calls for two types of observations:

Study of signals within a small unit when test inputs are given to the whole unit.

Isolation of a small element and doing local test to facilitate debugging.

Verilog has constructs to accommodate both types of observation through a hierarchical description of variables within.

# 1.10.1 Constructs for Modeling Timing Delays

Any basic gate has propagation delays and transmission delays associated with it. As the elements in the circuit increase in number, the type and variety of such delays increase rapidly; often one reaches a stage where the expected function is not realized thanks to an unduly large time delay. Thus there is a need to test every digital design for its performance with respect to time. Verilog has constructs for modeling the following delays:

Gate delay Net delay Path delay

#### Pin-to-pin delay

In addition, a design can be tested for setup time, hold time, clock-width time specifications, *etc*. Such constructs or delay models are akin to the finite delay time, rise time, fall time, path or propagation delays, *etc*., associated with real digital circuits or systems. The use of such constructs in the design helps simulate realistic conditions in a digital circuit. Further, one can change the values of delays in different ways. If a buffer capacity is increased, its associated delays can be reduced. If a design is to migrate to a better technology, the delay values can be rescaled. With such testing, one can estimate the minimum frequency of operation, the maximum speed of response, or typical response times.

## 1.10.2 SYSTEM TASKS

A number of system tasks are available in Verilog. Though used in a design description, they are not part of it. Some tasks facilitate control and flow of the testing process. The values of signals in a module can be displayed in the course of simulation. The tasks available for the purpose display them in desired formats. Reading data from specified files into a module and writing back into files are also possible through other tasks. Timescale can be changed prior to simulation with the help of specific tasks for the purpose.

A set of system functions add to the flexibility of test benches: They are of three categories:

## Functions that keep track of the progress of simulation time

Functions to convert data or values of variables from one format to another Functions to generate random numbers with specific distributions.

There are other numerous system tasks and functions associated with file operations, PLAs, etc.

1.10.3 PROGRAMMING LANGUAGE INTERFACE (PLI)

PLI provides an active interface to a compiled Verilog module. The interface adds a new dimension to working with Verilog routines from a C platform. The key functions of the interface are as follows:

One can read data from a file and pass it to a Verilog module as input. Such data can be test vectors or other input data to the module. Similarly, variables

in Verilog modules can be accessed and their values written to output devices. Delay values, logic values, *etc.*, within a module can be accessed and altered. Blocks written in C language can be linked to Verilog modules.

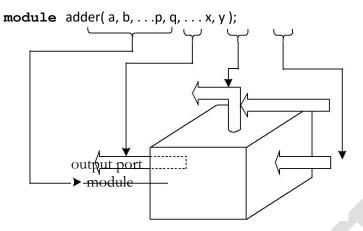

1.11 MODULE

Any Verilog program begins with a keyword – called a "module." A module is the name given to any system considering it as a black box with input and output terminals as shown in Figure 2.5. The terminals of the module are referred to as 'ports'. The ports attached to a module can be of three types:

IV B.Tech II-

Sem

input por

Figure Representation of a module as black box with its ports.

**input** ports through which one gets entry into the module; they signify the input signal terminals of the module.

**output** ports through which one exits the module; these signify the output signal terminals of the module.

**inout** ports: These represent ports through which one gets entry into themodule or exits the module; These are terminals through which signals are input to the module sometimes; at some other times signals are output from the module through these.

Whether a module has any of the above ports and how many of each type are present depend solely on the functional nature of the module. Thus one module may not have any port at all, another may have only input ports, while a third may have only output ports, and so on.

All the constructs in Verilog are centered on the module. They define ways of building up, accessing, and using modules. The structure of modules and the mode of invoking them in a design are discussed here.

A module comprises a number of "lexical tokens" arranged according to some predefined order. The possible tokens are of seven categories:

White spaces Comments Operators

**Numbers Strings**

**Identifiers Keywords**

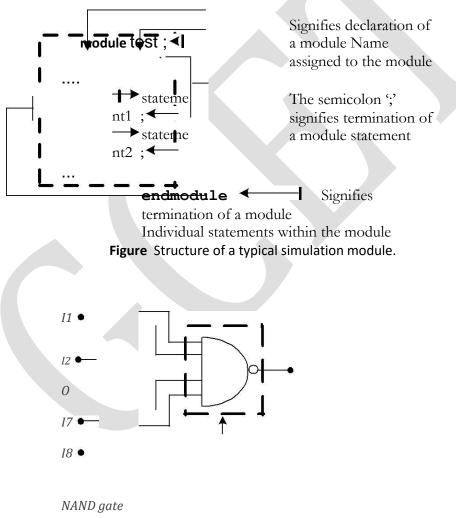

The rules constraining the tokens and their sequencing will be dealt with as we progress. For the present let us consider modules. In Verilog any program which forms a design description is a "module." Any program written to test a design description is also a "module." The latter are often

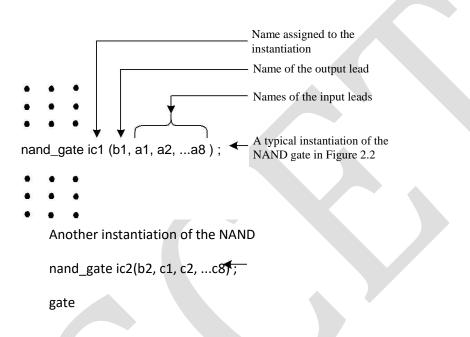

called as "stimulus modules" or "test benches." A module used to do simulation has the form shown in Figure 2.6. Verilog takes the active statements appearing between the "**module**" statement and the "**endmodule**" statement and interprets all of them together as forming the body of the module. Whenever a module is invoked for testing or for incorporation into a bigger design module, the name of the module ("test" here) is used to identify it for the purpose. A digression into design using SSI ICs is in order here. Consider the IC 7430, an eight input NAND gate. In any design using it, the IC can be looked up on as a black box with eight input leads and one output lead (Figure 2.7a). Three aspects characterize the IC – its function, its input leads, and its output lead. Other ICs may have more output leads. A NAND gate module is defined in an analogous manner in terms of its function, input leads and the output lead. The module used to describe the circuit here also follows the earlier format; that is, the "module" statement signifies the beginning of the module, the "endmodule" has to be more elaborate with the input and the output ports forming part of it (see Figure ).

**Figure (a)** Eight input NAND gate (IC 7430). Gate proper with terminals.

| Signifies declaration of a module(keyword)                                |

|---------------------------------------------------------------------------|

| Name assigned to the module                                               |

| Signifies the set of I/O leads to the module                              |

| <b>hodule</b> nand_gate (O, 1 <del>1, 12, 13, 14, 15, 16, 17, 18)</del> ; |

| <br>→ statement1 ; <                                                      |

| →statement2 ; <                                                           |

| endmodule                                                                 |

| Signifies termination of a module (keyword)                               |

| Individual statements within the module                                   |

| The semi-colon ';' signifies termination of a module statement            |

| Figure (b) Eight input NAND gate (IC 7430). Structure of the gate module. |

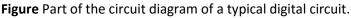

The same type of IC – 7430 – may be repeatedly used in a circuit. Each time it is used, a different name is assigned to it in the design sheet. Part of such a typical design sheet will look as in Figure 2.8. The associated table (Table 2.1) allows us to identify each type of IC to be used and put in its proper place. An automated design description can use a module defined above, repeatedly in a number of places as in the circuit of Figure . Each such use is an "instantiation." A typical instantiation of the module defined above has the form shown in Figure 2.9. The following observations are in order here:

Table Partial list of IC numbers and their types for a typical design

| IC No   | IC1  | IC2  | IC3 | <br>IC9  |  |

|---------|------|------|-----|----------|--|

| IC type | 7430 | 7430 |     | <br>7405 |  |

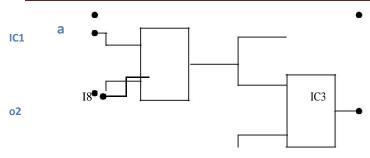

Figure Instantiations of modulenand\_gatein another module.

The designer has defined a specific function within a module; the module is assigned the name "nand\_gate."

The **nand\_gate** can be invoked (instantiated) by him in a design as many times as desired.

Each instantiation has to be assigned a separate identifier name by him (called "IC1", "IC2", *etc.*). As part of the instantiation declaration, the input and output terminals are to be defined. The convention followed is to stick to the same order as in the module declaration. It is further illustrated in Figure 2.9.

Some modules may have a large number of ports. Sticking to the order of the ports in an instantiation is likely to cause (human) errors. An alternative (and sometimes more convenient) form of instantiation is also possible – shown in Figure 2.10. The terminal identifications are explicit (though elaborate) here. Further one need not stick to the order of the ports as they appear in the

module definition. With such a form of port assignments, the possibility of errors is considerably reduced.

The following aspects of the modules and their instantiation are noteworthy:

Each module can be defined only once. Module definitions are to be done independently. One module cannot be defined inside another – they cannot be nested.

Any module can be instantiated inside another any number of times. Each instantiation has to be done with a separate name assigned to it.

The various constructs and features available in Verilog are discussed in the following chapters. However, certain conventions and constructs essential for the progress of the book at this stage are discussed in Chapter 3.

## 1.12 SIMULATION AND SYNTHESIS

A variety of Software tools related to VLSI design is available. We discuss here two of them directly relevant to us – Modelsim and Leonardo Spectrum of Mentor Graphics. Modelsim has been used to simulate the designs. Simulation results presented for the variety of examples discussed in the book have been obtained using it. Leonardo Spectrum has been used to obtain the synthesized circuits presented. We would like to draw the attention of the readers to the following in this context:

Only the essential aspects of the tools are presented – those essential for the progress of the book.

For more details of the tools and the variety of facilities they offer, one

can refer to the respective user manuals and the Help menus.

Tools from other sources are similar in essentials. Any of them can be used.

#### 1.12.1 Use of Modelsim SE 5.5

The procedure to invoke the tool and use it is briefly described here. The tool can be used to prepare a source file, edit and compile it, and simulate the compiled version.

Editing and Compilation

Open the Modelsim Window. We get the following menus listed at the top:

File Edit Design View Project Run Compare Macro

Click on "View." We get the following menus:

|   | All        |                    |

|---|------------|--------------------|

|   | Hide Works | bace               |

|   | Sources    |                    |

|   | Structure  |                    |

|   | Variables  |                    |

|   | Signals    |                    |

|   | List       |                    |

|   | Process    |                    |

|   | Wave       |                    |

|   |            |                    |

|   | Data flow  |                    |

|   |            |                    |

| D |            | IROUGH VERILOG HDL |

Data sets

New

Other

Click on "Source." The "Source" window opens with the following set of menus listed at the top:

| File    Edit    Object    Options    Window           |

|-------------------------------------------------------|

| Click on "File" option. We get the following options: |

| New                                                   |

| Open                                                  |

| Use source                                            |

| Source directory                                      |

| Properties                                            |

| Save                                                  |

| Save as                                               |

| Compile                                               |

| Close                                                 |

| Click on "New." We get the following options:         |

| VHDL                                                  |

|                                                       |

| Verilog                                               |

| Other                                                 |

Click on "Verilog." A "Source\_edit-new.v" opens.

The Verilog design can be keyed in. It forms the source file. The source file considered in various examples in the book can be created in this manner

(e.g., Example 4.2 and Figure 4.4).

Click on "File" option. We get a pull down menu. Click on "Save as."

Select a Directory of your choice. Give a suitable filename with extension ".v" (Say "demo.v"). Click on "Save" and save the file. The source (design) file has been created and saved. Now it is ready for compilation.

Click on "Compile." "Compile HDL Source Files" window opens. File name "demo" is displayed. Library "Work" is displayed. The selected file (demo.v) will be compiled and loaded into Work. The lines of display in the

main window confirm this.

If the source file has any syntax or logical errors, compilation will not take place. The errors will be indicated in the main window. The source file can be opened (by clicking on the main menu) and edited. Once again compilation can be attempted. The procedure has to be repeated iteratively until all the errors in the source file have been removed and compilation is successfully completed.

#### Simulation

In the main window click on "Design" pulldown menu. In the options displayed, click on "Load Design." The following options are displayed at the top:-

Design VHDL Verilog Libraries SDF

Select "Design" and click on it. A small window appears on the screen. "Library: Work" is displayed, implying that the working library is open. The module name "demo" is displayed under it. In the normal course the names of all the compiled files will be listed alphabetically one below the other. The

specific file to be simulated is to be selected by clicking on the same.

The "Load" button below gets highlighted. Click on it. The design gets loaded and is ready for simulation run.

Click the "Run" menu in the Modelsim main window. Select 100 ns runtime. The design runs for 100 ns (by default) and the output list appears in the main window. The listing can be selected, copied, and pasted to another file. The simulation results for the various examples in

the book have been obtained in this manner. If necessary, the time duration of simulation can be altered in

the main window.

Observing Waveforms

Simulation results can alternately be viewed as waveforms with the following procedure:

In the main Modelsim window click on "Signals." The signals window opens with the following options displayed at the top:

File Edit View Window

Click on the "View" pulldown menu. We get the options as shown below: Wave List Log Filter

Amongst the options available, click on "Wave." We get the following options:

Selected Signals Signals in Region Signals in Design

Select <u>"Signals in Desig</u>n." The "Waveform Window" opens and shows the signals in the design. The Window has a "Run" option.

Click on "Run" to run the design and get the waveforms displayed. The waveforms shown as simulated outputs for different examples in the book have been obtained in this manner.

One can practice simulation of a few examples given in the book. Subsequently options available at the different stages can be tried, and the tool with its full versatility can be mastered.

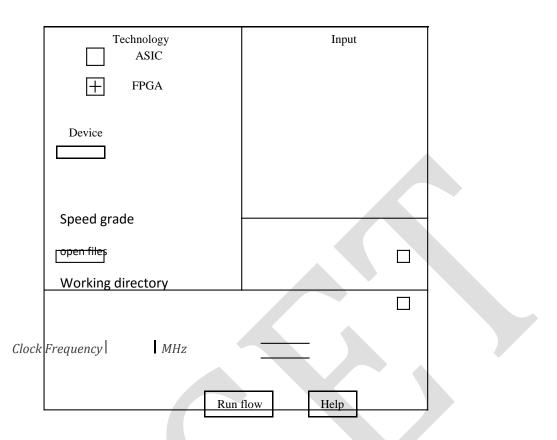

## 1.12.2 Synthesis

Conversion of the code into hardware logic and fitting it into an FPGA or ASIC to realize the circuit is termed "Synthesis." We have used the Mentor Graphics Synthesis tool called "Leonardo Spectrum" for the purpose. The synthesis procedure is briefly described here:

Double click on "Leonardo Spectrum 2000.1b."

The Main Window named "Examplar Logic – Leonardo Spectrum Level 3" opens with a pulldown menu as follows:

File Edit View Tools Window Help

Click on "File". A pulldown menu opens with options such as the following:

Sem

Select "New." A window named "untitled" opens. We can type in a new program and save it as a file with a name assigned to it (Say "name.v") in a directory of our choice. The procedure is similar to that followed above to create and save a new file with extension ".v" (signifying that it is a Verilog file). The file is now ready for synthesis. However, it is always preferable to simulate a file and be fully satisfied with at the simulation stage itself before

synthesizing it.

Click on the "Tools" menu on the main window. A set of options appear on the screen.

Select "Quick Set up." A window of the type shown in Figure 2.11 appears. All the settings necessary to complete the synthesis can be carried out with it. Click on "Open files." Select the Verilog source file to be synthesized. It will

be visible under "Input" in the figure.

Under "Technology" select "FPGA." Select a device of (say) Xilinx – for example, XC4000XL. The selected Xilinx device name is displayed under

'Device'.

Select a "Clock Frequency" – say 10 MHz.

Click on the "Run Flow" button. The synthesis program runs and completes

the synthesis. Summarized results will be displayed on the screen.

If the coding is correct and synthesizable, the display "Ready" appears highlighted at the bottom left-hand corner. If not, error details will be displayed. The program may be rectified and synthesis attempted again. Icons for "RTL Schematic", "Gate Level Schematic" and "Critical Path

Schematic" at the top become active.

We can click on each of them in succession. The circuit schematic can be viewed at the RTL level or the gate level. The critical path can be viewed – it represents the path that takes the maximum time of operation on a pin-to-pin basis. It sets the upper limit to the speed of operation of the circuit.

The synthesized circuits shown for the different examples in the book have been obtained in this manner. The device selected to synthesize the design, is called the "Target Device." One can select any other suitable target device of Xilinx or other FPGA vendors like Actel, Altera, Cypress, Lattice, Lucent, Quicklogic, *etc*.

The program generates a summary of the synthesis activity and displays it as a "Sum File." It gives a report on the utilization of the "Target Device" by the

Sem

#### Figure 2.11 The Window in Leonardo Spectrum to do the settings for synthesis.

design that was synthesized. It also generates and displays some timing information like "Critical Path Timing."

#### 1.13 TEST BENCHES

Any digital circuit that has been designed and wired goes through a testing process before being declared as ready for use. Testing involves studying circuit behavior under simulated conditions for the following: Check and ensure that all functions are carried out as desired. It is the test for the static behavior of the circuit. A set of logic input values are applied at

selected points and the logic values at another set of points observed.

Check and ensure that all the functional sequences are carried out as desired. It is one of the tests for the dynamic behavior of the circuit. It may call for the

generation of specific input sequences with respect to time, applying them to the circuit and observing selected outputs.

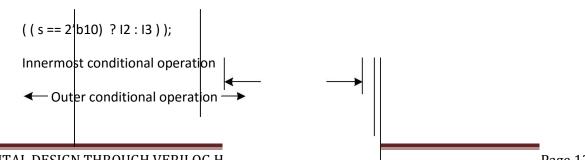

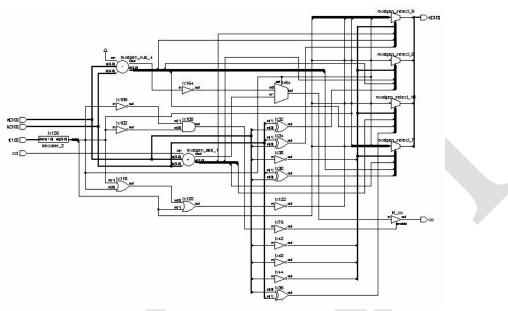

Check for the timing behavior: One tests for the propagation and other types of delays here. A variety of tests may have to be carried out. It may involve observation of variations in the signals at selected points, measuring the time delay between specified events, measuring pulse widths, and so on.