# MPMC Course File

# Contents required for course file

- 1. Cover Page

- 2. Syllabus copy

- 3. Vision of the Department

- 4. Mission of the Department

- 5. PEOs and POs

- 6. Course objectives and outcomes

- 7. Brief notes on the importance of the course and how it fits into the curriculum

- 8. prerequisites

- 9. Instructional Learning Outcomes

- 10. Course mapping with PEOs and POs

- 11. Class Time Table

- 12. Individual Time Table

- 13. Micro Plan with dates and closure report

- 14. Detailed notes

- 15. Additional topics

- 16. University Question papers of previous years

- 17. Question Bank

- 18. Assignment topics

- 19. Unit wise Quiz Questions

- 20. Tutorial problems

- 21. Known gaps, if any

- 22. Discussion topics

- 23. References, Journals, websites and E-links

- 24. Quality Control Sheets

- 25. Student List

- 26. Group-Wise students list for discussion topics

# 1.cover page

# GEETHANJALI COLLEGE OF ENGINEERING AND TECHNOLOGY

# **DEPARTMENT OF** *Electronics and Communication Engineering*

(Name of the Subject ): Microprocessors and Microcontrollers Course file

(JNTU CODE – A60430) Programme : UG

Branch: ECE Version No : 0

Year: III Document No: GCET/ECE/56012/01

Semester: II No. of pages :

Classification status (Unrestricted / Restricted ) : Unrestricted

Distribution List: Dept. Library, Dept Office, Concerned Faculty

Prepared by

1) Name: M.Laxmi/ P.Sneha Naga Shilpa/D.Sony/M.V.Sireesha

2) Sign :

3) Design: Assoc. Professor/Asst. Professors

4) Date : 25/11/2015

Verified by : 1) Name : \* For Q.C Only.

2) Sign :

3) Design : 2) Sign :

4) Date : 3) Design :

4) Date :

1) Name:

Approved by: (HOD) 1) Name: Dr.P.Sri Hari

2) Sign :

3) Date :

# 2. Syllabus copy

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY III YEAR B.TECH.ECE-IISEM

# (A60430) MICROPROCESSORS AND MICROCONTROLLERS

# **Course Objective:**

The course objectives are:

• To develop an in-depth understanding of the operation of microprocessor and microcontrollers, machine language programming and interfacing techniques

### **UNIT-1**

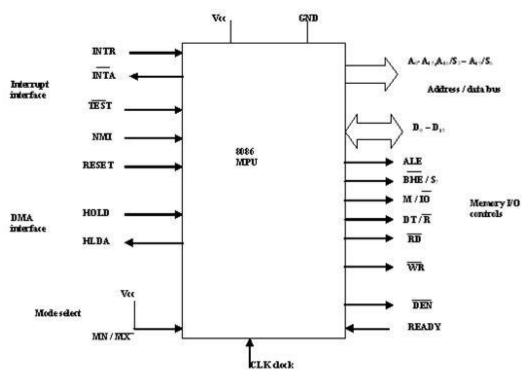

**8080 Architecture:** 8086 Architecture–functional diagram, Register organization, memory segmentation, Programming model, memory addresses, Physical memory organization, Architecture of 8086, Signal description of 8086, Common function signals, Timing diagrams, Interrupts of 8086.

### **UNIT-II**

**Instruction set and assembly language programming of 8086:** Instruction formats, addressing modes, Instruction set, Assembler directives, macros, Simple programs involving logical, branch and call instructions, sorting, evaluating arithmetic expressions, string manipulations.

### UNIT-III

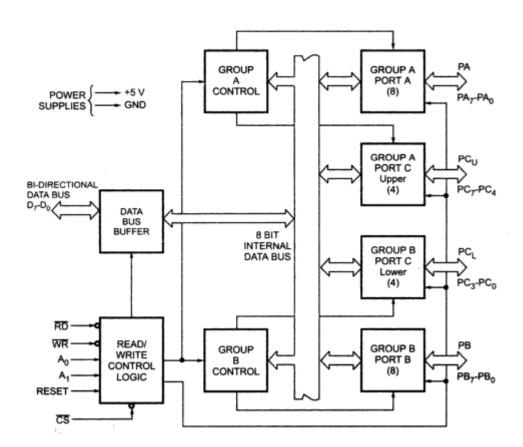

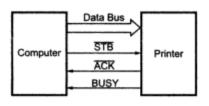

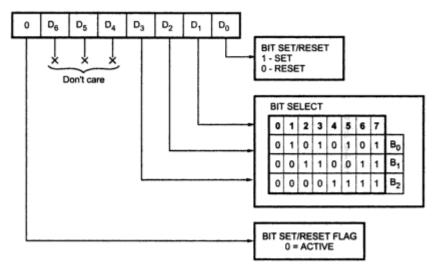

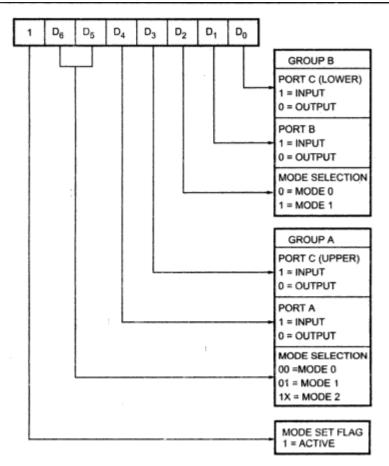

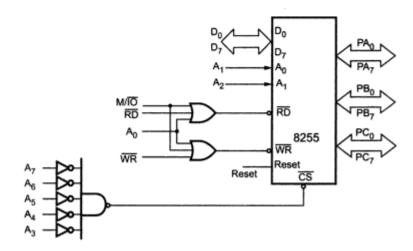

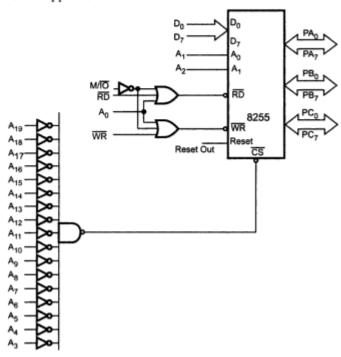

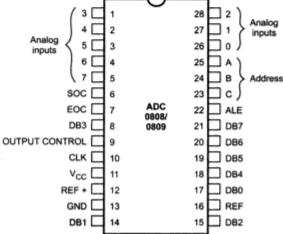

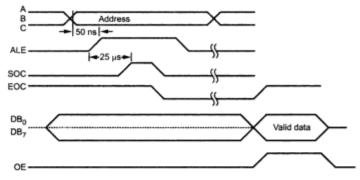

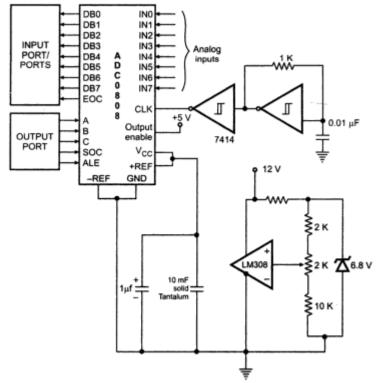

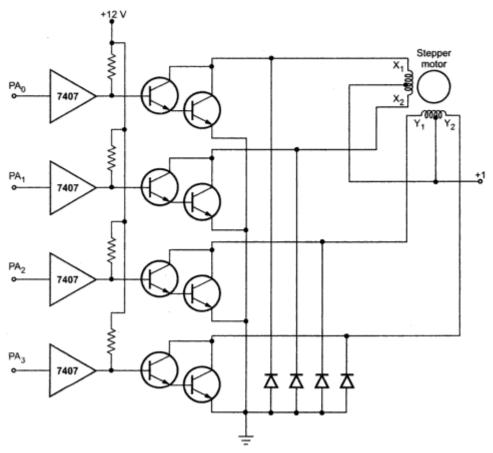

**I/O interface:** 8255-PPI, various Modes of operation and interfacing to 8086, Modes of operation and interfacing to 8086, Interfacing keyboard, display, D/A and A/D converter.

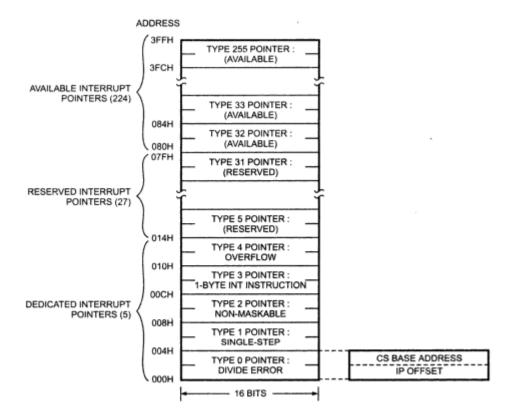

**Interfacing with advanced devices:** Memory interfacing to 8086, Interrupt structure of 8086, vector interrupt table, interrupt service routine.

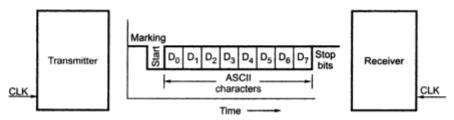

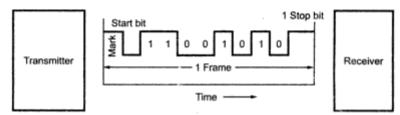

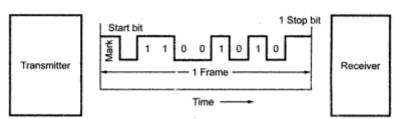

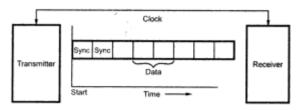

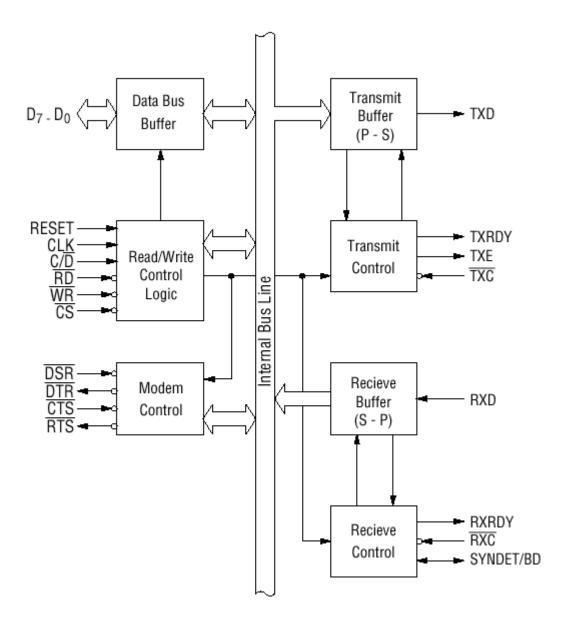

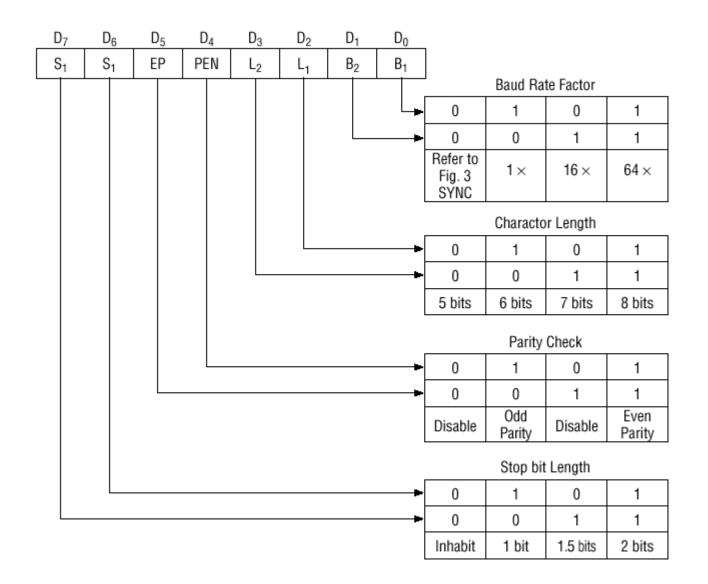

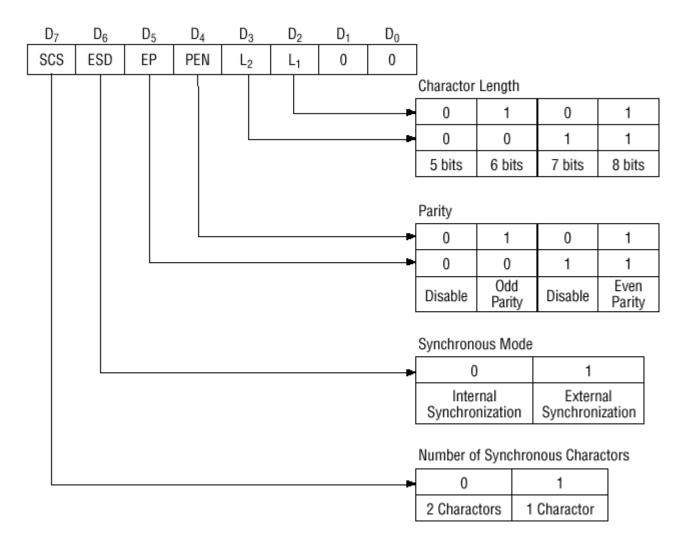

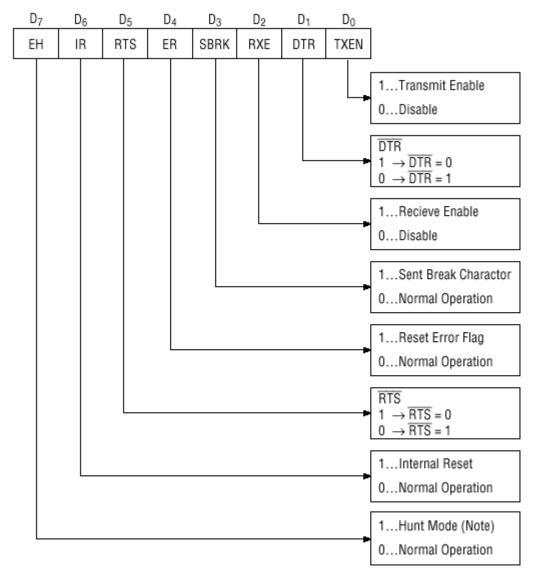

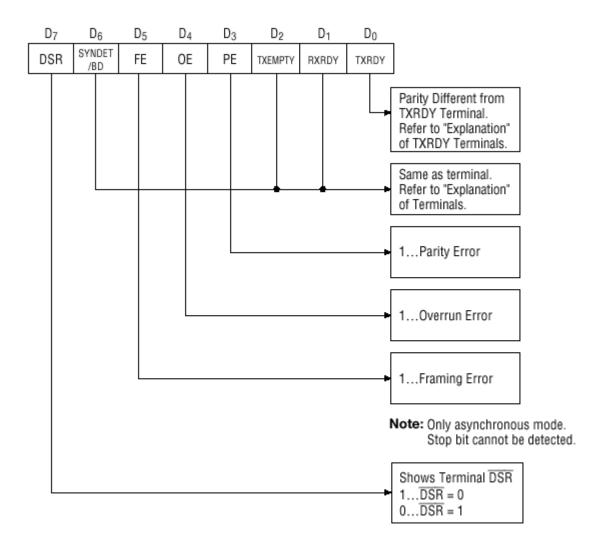

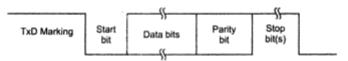

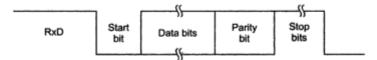

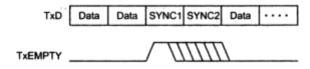

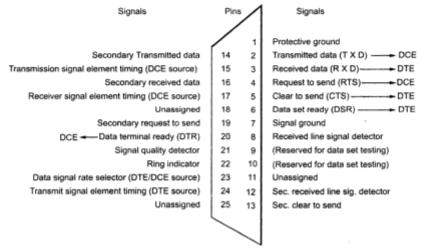

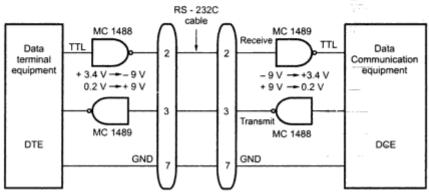

**Communication interface:** Serial communication standards, serial data transfer schemes, 8251 USART architecture and interfacing.

## **UNIT-IV**

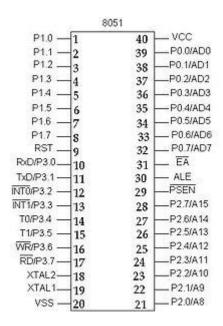

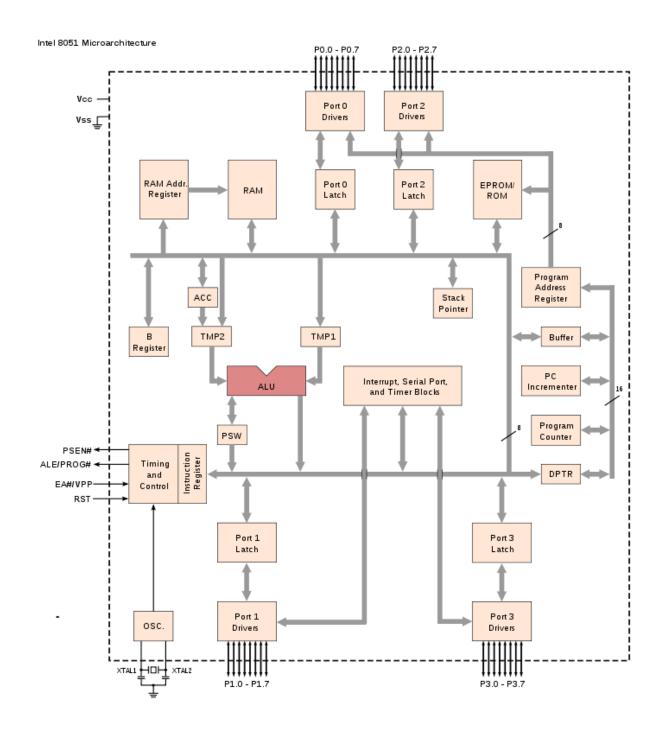

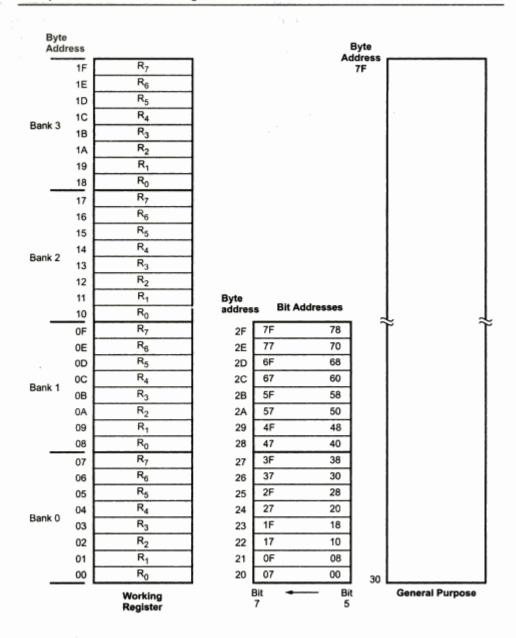

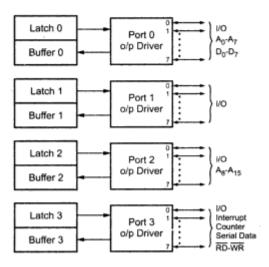

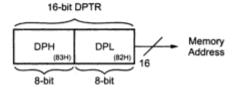

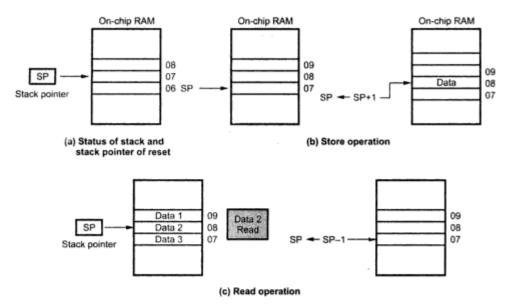

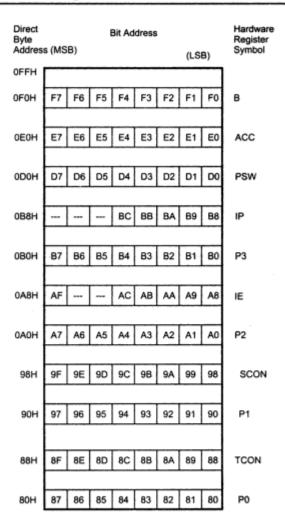

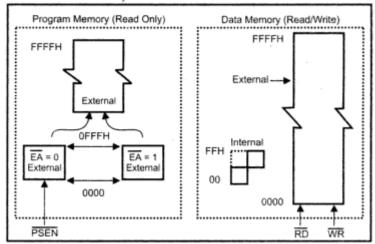

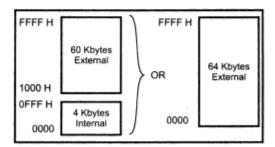

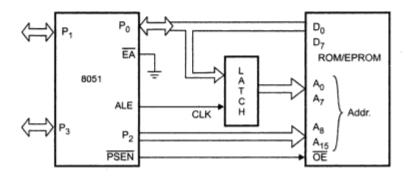

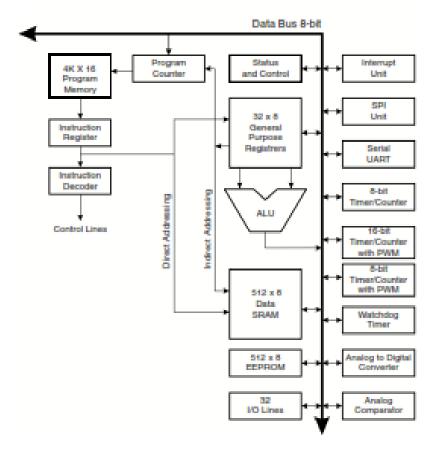

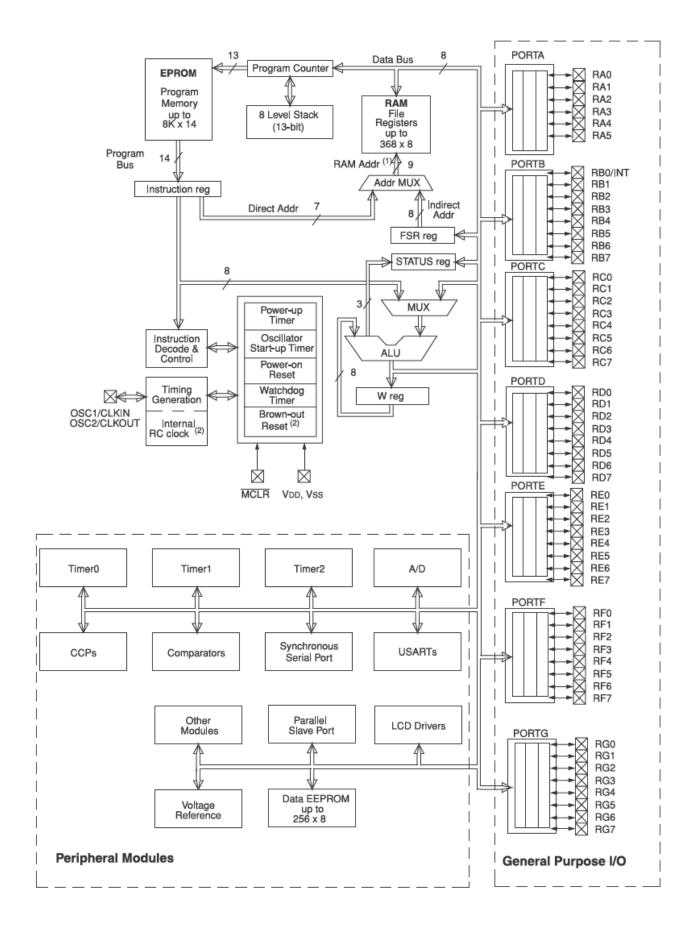

**Introduction to microcontrollers:** Overview of 8051 microcontrollers, Architecture, I/O ports, memory organization, Addressing modes, Instruction set of 8051, Simple programs.

### **UNIT-V**

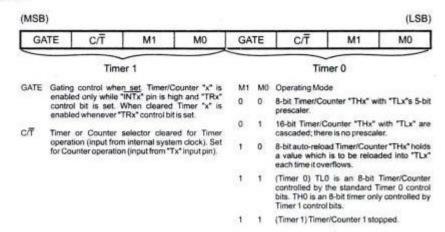

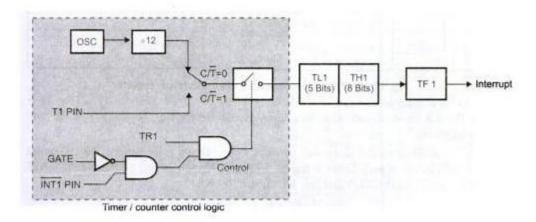

**8051 real time control:** Programming timer interrupts, Programming external hardware interrupts, Programming the serial communication interrupts, Programming 8051 timers/counters.

### **Course Outcome:**

Upon completion of the course:

- The student will learn the internal organization of popular 8086/8051 microprocessors/microcontrollers.

- The student will learn hardware and software interaction and integration.

- The students will learn the design of microprocessors/microcontrollers- based systems.

# 3. Vision of the Department

To impart quality technical education in Electronics and Communication Engineering emphasizing analysis, design/synthesis and evaluation of hardware/embedded software using various Electronic Design Automation (EDA) tools with accent on creativity, innovation and research thereby producing competent engineers who can meet global challenges with societal commitment.

# 4. Mission of the Department

- i. To impart quality education in fundamentals of basic sciences, mathematics, electronics and communication engineering through innovative teaching-learning processes.

- To facilitate Graduates define, design, and solve engineering problems in the field of Electronics and Communication Engineering using various Electronic Design Automation (EDA) tools.

- iii. To encourage research culture among faculty and students thereby facilitating them to be creative and innovative through constant interaction with R & D organizations and Industry.

- iv. To inculcate teamwork, imbibe leadership qualities, professional ethics and social responsibilities in students and faculty

# 5.PEOs and POs

# **Program Educational Objectives of B. Tech (ECE) Program:**

- I. To prepare students with excellent comprehension of basic sciences, mathematics and engineering subjects facilitating them to gain employment or pursue postgraduate studies with an appreciation for lifelong learning.

- II. To train students with problem solving capabilities such as analysis and design with adequate practical skills wherein they demonstrate creativity and innovation that would enable them to develop state of the art equipment and technologies of multidisciplinary nature for societal development.

- III. To inculcate positive attitude, professional ethics, effective communication and interpersonal skills which would facilitate them to succeed in the chosen profession exhibiting creativity and innovation through research and development both as team member and as well as leader.

# **Program Outcomes of B.Tech ECE Program**

- An ability to apply knowledge of Mathematics, Science, and Engineering to solve complex engineering problems of Electronics and Communication Engineering systems.

- 2. An ability to model, simulate and design Electronics and Communication Engineering systems, conduct experiments, as well as analyze and interpret data and prepare a report with conclusions.

- An ability to design an Electronics and Communication Engineering system, component, or process to meet desired needs within the realistic constraints such as economic, environmental, social, political, ethical, health and safety, manufacturability and sustainability.

- 4. An ability to function on multidisciplinary teams involving interpersonal skills.

- 5. An ability to identify, formulate and solve engineering problems of multidisciplinary nature.

- 6. An understanding of professional and ethical responsibilities involved in the practice of Electronics and Communication Engineering profession.

- 7. An ability to communicate effectively with a range of audience on complex engineering problems of multidisciplinary nature both in oral and written form.

- 8. The broad education necessary to understand the impact of engineering solutions in a global, economic, environmental and societal context.

- 9. A recognition of the need for, and an ability to engage in life-long learning and acquire the capability for the same.

- 10. A knowledge of contemporary issues involved in the practice of Electronics and Communication Engineering profession

- 11. An ability to use the techniques, skills and modern engineering tools necessary for engineering practice.

- 12. An ability to use modern Electronic Design Automation (EDA) tools, software and electronic equipment to analyze, synthesize and evaluate Electronics and Communication Engineering systems for multidisciplinary tasks.

- 13. Apply engineering and project management principles to one's own work and also to manage projects of multidisciplinary nature.

# 6.. Course objectives and outcomes

# **Course objectives:**

- 1. To understand the basic 8, 16 bit microprocessor architecture and its functionalities.

- 2. To understand the programming model of microprocessor.

- 3. To develop the microprocessor based programs for various applications.

- 4. To make the interfacing in between microprocessor and various peripherals.

- 5. To develop DOS/BIOS programs.

- 6. To develop the microcontroller based programs for various applications.

- 7. To enable the students to understand basic feature of 8051 and AVR controller

# course outcomes:

- **CO 1**: Basic understanding of 8085 and 8086 microprocessors architectures and its functionalities.

- **CO 2**: Design and develop 8086 Microprocessor based systems for real time applications using low level language like ALP

- **CO** 3: Interface external peripherals and I/O devices and program the 8086 microprocessor.

- CO 4: To write Interrupt service Routine(ISR) to handle interrupts in 8086 microprocessor.

- **CO 5**: To transmit data serially in Multi-processor applications

- CO 6: Basic understanding of 8051 microcontrollers architectures and its functionalities.

- **CO 7**: Design and develop microcontroller based systems for real time applications using low level language like ALP

- **CO 8**: To distinguish between RISC and CISC microcontrollers and Analyze the architecture of AVR family microcontroller

# 7. Brief notes on the importance of the course and how it fits into the curriculum

- 1. The student will be able to understand the basic microprocessors architecture its functionality and to interface with I/O devices.

- 2. This courset will gives the knowledge to understand the advanced processors and its interfacing with various devices.

- 3. It will be the base for embedded system design.

- 4. The course will be usefull for understanding computer organization and advanced systems.

**8.Pre Requisites:** Switching Theory & Logic Design ,Computer Organization.

# **9.Instructional Learning Outcomes**

# UNIT - I

- 1. Student understands the architecture of 8085 and 8086 processor.

- 2. Student understands the read (input) and write (output) of data to or from the memory.

- 3. Student gets complete knowledge of registers and memory system of 8086 processor.

- 4. Student understands the single and multi-processor mode of 8086 processor.

# UNIT – II

- 1. Student understands the various instruction formats of 8086 processor and can convert assembly language code into machine language code.

- 2. Student understands the various addressing modes required for assembly language programming and can calculate the physical address.

- 3. Student can develop various assembly language programs in real time applications using microprocessor.

# UNIT –III

- 1. Student understands the architecture of 8255 PPI.

- 2. Student understands the various command words and modes of operation of 8255 PPI.

- Student can develop real-time interfacing devices and interface them with 8086 processor for wider applications.

- 4. Student can develop the interfacing of memory (RAM, ROM, PROM, EEPROM) with 8086 processor.

- 5. Student understands interrupt structure, interrupt vector table and interrupt service routines etc.

- 6. Student understands the architecture of 8251USART.

**7.** Student understands the various command words, modes of operation and interfacing of 8251 USART with 8086 processor.

# <u>UNIT –IV</u>

- 1. Student understands the architecture of 8051 microcontroller.

- 2. Student understands the addressing modes and instruction set of 8051 microcontroller.

- 3. Student can develop various assembly language programs in real time applications using microcontrollers.

# UNIT -V

- Student can develop the programming of timers/counters of 8051 microcontroller in real time systems.

- 2. Student can develop the programming of interrupts of 8051 microcontroller in real time systems.

- Student can develop the programming of serial communication interrupts of 8051 microcontroller in real time systems.

# 10.Course mapping with PEOs and POs

Course mapping with PO's

| Course Outcomes                        | Program outcomes |   |   |   |   |   |   |   |   |    |    |    |    |

|----------------------------------------|------------------|---|---|---|---|---|---|---|---|----|----|----|----|

|                                        | 1                | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 |

| CO 1: Basic understanding of 8085 and  |                  | 2 |   | 2 | 2 |   |   |   |   |    |    | 1  |    |

| 8086 microprocessors architectures and |                  |   |   |   |   |   |   |   |   |    |    |    |    |

| its functionalities                    |                  |   |   |   |   |   |   |   |   |    |    |    |    |

| CO 2: Design and develop               |                  | 2 |   | 2 | 2 |   |   |   |   |    |    | 1  |    |

| Microprocessor based systems for real  |                  |   |   |   |   |   |   |   |   |    |    |    |    |

| time applications using low level      |                  |   |   |   |   |   |   |   |   |    |    |    |    |

| language like ALP                      |                  |   |   |   |   |   |   |   |   |    |    |    |    |

|                                        |                  |   |   |   |   |   |   |   |   |    |    |    |    |

| CO 3: Interface external peripherals   |                  | 2 |   | 2 | 2 |   |   |   |   |    |    | 1  |    |

| and I/O devices and program the 8086   |                  |   |   |   |   |   |   |   |   |    |    |    |    |

| microprocessor.                        |                  |   |   |   |   |   |   |   |   |    |    |    |    |

| CO 4: To write Interrupt service<br>Routine(ISR) to handle interrupts in<br>8086 microprocessor.                             | 2 | 2 | 2 |  |  | 1 |  |

|------------------------------------------------------------------------------------------------------------------------------|---|---|---|--|--|---|--|

| CO 5: To transmit data serially in Multi-processor applications                                                              | 2 | 2 | 2 |  |  | 1 |  |

| CO 6: Basic understanding of 8051 microcontrollers architectures and its functionalities                                     | 2 | 2 | 2 |  |  | 1 |  |

| CO 7: Design and develop<br>microcontroller based systems for real<br>time applications using low level<br>language like ALP | 2 | 2 | 2 |  |  | 1 |  |

| CO 8: To distinguish between RISC and CISC microcontrollers and Analyze the architecture of AVR family microcontroller       | 2 | 2 | 2 |  |  | 1 |  |

# Course mapping with PEOs

|                                                                                                                                                                                                                    | PRO                         | GRAMME                             | E EDUC                    | CATIONAL                           | OBJEC'                       | TIVES                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------|---------------------------|------------------------------------|------------------------------|------------------------------------|

| a) an ability to apply                                                                                                                                                                                             | Domai<br>n<br>knowle<br>dge | Professi<br>onal<br>Employ<br>ment | High<br>er<br>Degr<br>ees | Enginee<br>ring<br>citizensh<br>ip | Lifelo<br>ng<br>Learn<br>ing | Research<br>and<br>Develop<br>ment |

| the knowledge of Mathematics, science and engineering in Electronics and communications                                                                                                                            | V                           | $\checkmark$                       | √                         | V                                  | <b>√</b>                     | V                                  |

| b) an ability to Design & Conduct Experiments, as well as analyze & Interpret Data                                                                                                                                 | V                           | V                                  | V                         | V                                  | V                            | V                                  |

| c) an ability to design a system, component, or process to meet desired needs with in realistic constraints such as economic, environmental, social, political, ethical, health and safety, manufacturability, and | <b>V</b>                    | V                                  | V                         |                                    | V                            | √                                  |

| sustainability                                                                                                                                |          |           |          |           |           |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|----------|-----------|-----------|----------|

| d) an ability to function<br>on multidisciplinary<br>teams                                                                                    | V        | V         |          |           | V         | <b>√</b> |

| e) an ability to Identify, Formulate & Solve problems in the area of Electronics and Communications Engineering                               | <b>√</b> | <b>√</b>  | √        |           | <b>V</b>  | V        |

| h) the broad education necessary to understand the impact of engineering solutions in a global, economic, environmental, and societal context | <b>V</b> | <b>√</b>  | <b>V</b> |           | <b>V</b>  | <b>√</b> |

| i) a recognition of the<br>need for, and an ability<br>to engage in life-long<br>learning                                                     | V        | $\sqrt{}$ | V        | $\sqrt{}$ | $\sqrt{}$ | V        |

| k) an ability to use the<br>techniques, skills, and<br>modern engineering<br>tools necessary for<br>engineering practice                      | V        | V         | V        | V         | V         | V        |

# 12. Class Time Table

Hard copies are attached

# 13.Micro Plan:

$Name\ of\ the\ Faculty M. Laxmi/P. Sneha\ Naga\ Shilpa/D. Sony/M. V. Sireesha$

**Branch: ECE**

Year & Sem: III-II

**Subject: Microprocessors and microcontrollers**

# **Lesson Plan**

| S.L<br>no | Unit<br>No | Total no of<br>Periods | Topics to be covered                                                            | Reg/<br>Additional | Teaching aids<br>LCD/OHP/BB | Remarks |

|-----------|------------|------------------------|---------------------------------------------------------------------------------|--------------------|-----------------------------|---------|

| 1         | 1          | 11                     | Overview of basics from Switching Th                                            | Additional         | BB                          |         |

|           |            |                        | Logic Design and Computer Organizat                                             |                    |                             |         |

| 2         |            |                        | Overview of MPMC syllabus and its importance in Real world                      | Additional         | BB                          |         |

| 3         |            |                        | Evolution of microprocessors and Introduction to 8085 microprocessor,           | Additional         | OHP,BB                      |         |

| 4         |            |                        | Architecture of 8086 Microprocessor – functional diagram description            | Regular            | OHP,BB                      |         |

| 5         |            |                        | Register organization, memory segmentation                                      | Regular            | OHP,BB                      |         |

| 6         |            |                        | Programming model, memory addresses                                             | Regular            | OHP,BB                      |         |

| 7         |            |                        | Physical memory organization                                                    | Regular            | BB                          |         |

| 8         |            |                        | Signal description of 8086, Common function signals                             | Regular            | BB                          |         |

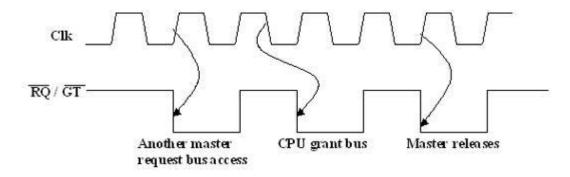

| 9         |            |                        | maximum and minimum mode signals                                                | Regular            | BB                          |         |

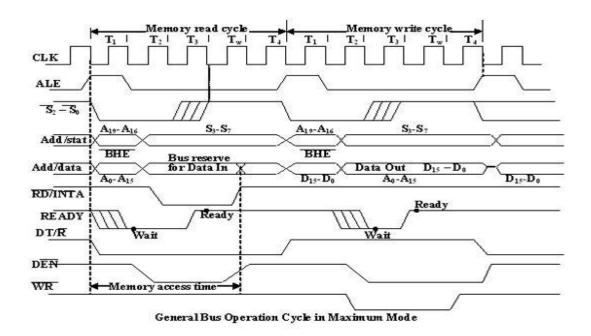

| 10        |            |                        | Timing diagrams, Interrupts of 8086                                             | Regular            | OHP,BB                      |         |

| 11        |            |                        | Tutorial class                                                                  | Regular            | BB                          |         |

| 12        | II         | 08                     | Instruction formats, addressing modes                                           | Regular            | OHP,BB                      |         |

| 13        |            |                        | Instruction set of 8086                                                         | Regular            | BB                          |         |

| 14        |            |                        | Instruction set of 8086                                                         | Regular            | BB                          |         |

| 15        |            |                        | Assembler directives, macros                                                    | Regular            | OHP,BB                      |         |

| 16        |            |                        | Simple programs on logical ,branch and call instructions                        | Regular            | BB                          |         |

| 17        |            |                        | Programs on sorting, string manipulations                                       | Regular            | BB                          |         |

| 18        |            |                        | Tutorial class                                                                  | Regular            | BB                          |         |

| 19        |            |                        | Introduction to Pentium and dual core processors                                | Additional         | OHP,BB                      |         |

| 20        | III        | 20                     | Introduction to parallel data transfer methods and importance of port structure | Regular            | OHP,BB                      |         |

| 21        |            |                        | 8255-PPI                                                                        | Regular            | OHP,BB                      |         |

| 22        |            |                        | Modes of operation and interfacing to 8086                                      | Regular            | BB                          |         |

| 23        |            |                        | Modes of operation and interfacing to 8086                                      | Regular            | BB                          |         |

| 24        |            |                        | Interfacing keyboard, display to 8086                                           | Regular            | OHP,BB                      |         |

| 25 |    |    | Stepper motor interfacing to 8086                             | Missing    | BB         |

|----|----|----|---------------------------------------------------------------|------------|------------|

| 26 |    |    | A/D converter interfacing to 8086                             | Regular    | OHP,BB     |

| 27 |    |    | D/A converter interfacing to 8086                             | Regular    | BB         |

| 28 |    |    | Tutorial class                                                | Regular    | LCD,OHP,BB |

| 29 |    |    | Memory interfacing to 8086                                    | Regular    | ОНР,ВВ     |

| 30 |    |    | Memory interfacing to 8086                                    | Regular    | BB         |

| 32 |    |    | Interrupt structure of 8086, vector                           | Regular    | OHP,BB     |

|    |    |    | interrupt table, interrupt service routine                    |            |            |

| 34 |    |    | Introduction to DOS and BIOS                                  | Missing    | BB         |

|    |    |    | interrupts                                                    |            |            |

| 35 |    |    | Interrupt controller-8259, Interfacing                        | Additional | BB         |

|    |    |    | DMA controller 8257 to 8086                                   |            |            |

| 36 |    |    | Tutorial class                                                | Regular    | OHPBB      |

| 37 |    |    | 8251 USART architecture                                       | Regular    | BB         |

|    |    |    | 8251 USART interfacing                                        | Regular    | BB         |

| 38 |    |    | RS-232,IEEE 488 Standards                                     | Missing    | OHP,BB     |

| 39 |    |    | Prototyping and troubleshooting                               | Missing    | OHP,BB     |

| 40 |    |    | TTL to RS 232 and                                             | Missing    | BB         |

|    |    |    | RS-232 to TTL conversion                                      |            |            |

| 41 | IV | 08 | Overview of 8051 microcontrollers                             | Regular    | OHP,BB     |

| 42 |    |    | Architecture of 8051microcontroller                           | Regular    | BB         |

| 43 |    |    | I/O ports, memory segmentation of 8051                        | Regular    | BB         |

| 44 |    |    | Addressing modes of 8051                                      | Regular    | BB         |

| 45 |    |    | Instruction set of 8051                                       | Regular    | BB         |

| 46 |    |    | Simple programs on 8051                                       | Regular    | BB         |

| 47 |    |    | Simple programs on 8051                                       | Regular    | OHP,BB     |

| 49 |    |    | Tutorial class                                                | Regular    | OHP,BB     |

| 50 | V  | 10 | Interrupts of 8051 microcontroller                            | Regular    | OHP,BB     |

| 51 |    |    | Timer/counters of 8051                                        | Regular    | BB         |

| 52 |    |    | Serial communication of 8051                                  | Regular    | BB         |

| 53 |    |    | Programming timer interrupts                                  | Regular    | OHP,BB     |

| 54 |    |    | Programming external hardware                                 | Regular    | OHP,BB     |

| 55 |    |    | interrupts Programming the serial communication               | Regular    | BB         |

| 33 |    |    | interrupts                                                    | Regulai    | DD         |

| 56 |    |    | Programming 8051 timers/counters                              | Regular    | BB         |

| 57 |    |    | Tutorial class                                                | Regular    | BB         |

| 58 |    |    | Distinguish between RiSC vs CISC.  AVR RISC microcontroller – | Additional | OHP,BB     |

|    |    |    | architecture                                                  |            |            |

| 59 | †  |    | Introduction to PIC and ARM                                   | Additional | OHP,BB     |

|    |    |    | controllers                                                   |            |            |

# Micro Plan:ECE-A

| SL.<br>No | Unit<br>No. | Total<br>No.o<br>Perio<br>ds | Date | Topic to be covered in One lecture                                              | Regular/<br>Additional/<br>missing | Teaching<br>aids<br>LCD/OHP/<br>BB | Remarks |

|-----------|-------------|------------------------------|------|---------------------------------------------------------------------------------|------------------------------------|------------------------------------|---------|

| 1         | 1           | 11                           |      | Overview of basics from Switching The Logic Design and Computer Organization.   | Additional                         | BB                                 |         |

| 2         |             |                              |      | Overview of MPMC syllabus and its importance in Real world                      | Additional                         | BB                                 |         |

| 3         |             |                              |      | Evolution of microprocessors and<br>Introduction to 8085 microprocessor,        | Additional                         | OHP,BB                             |         |

| 4         |             |                              |      | Architecture of 8086 Microprocessor – functional diagram description            | Regular                            | OHP,BB                             |         |

| 5         |             |                              |      | Register organization, memory segmentation                                      | Regular                            | OHP,BB                             |         |

| 6         |             |                              |      | Programming model, memory addresses                                             | Regular                            | OHP,BB                             |         |

| 7         |             |                              |      | Physical memory organization                                                    | Regular                            | BB                                 |         |

| 8         |             |                              |      | Signal description of 8086, Common function signals                             | Regular                            | BB                                 |         |

| 9         |             |                              |      | maximum and minimum mode signals                                                | Regular                            | BB                                 |         |

| 10        |             |                              |      | Timing diagrams, Interrupts of 8086                                             | Regular                            | OHP,BB                             |         |

| 11        |             |                              |      | Tutorial class                                                                  | Regular                            | BB                                 |         |

| 12        | II          | 08                           |      | Instruction formats, addressing modes                                           | Regular                            | OHP,BB                             |         |

| 13        |             |                              |      | Instruction set of 8086                                                         | Regular                            | BB                                 |         |

| 14        |             |                              |      | Instruction set of 8086                                                         | Regular                            | BB                                 |         |

| 15        |             |                              |      | Assembler directives, macros                                                    | Regular                            | OHP,BB                             |         |

| 16        |             |                              |      | Simple programs on logical ,branch and call instructions                        | Regular                            | BB                                 |         |

| 17        |             |                              |      | Programs on sorting, string manipulations                                       | Regular                            | BB                                 |         |

| 18        |             |                              |      | Tutorial class                                                                  | Regular                            | BB                                 |         |

| 19        |             |                              |      | Introduction to Pentium and dual core processors                                | Additional                         | OHP,BB                             |         |

| 20        | III         | 20                           |      | Introduction to parallel data transfer methods and importance of port structure | Regular                            | OHP,BB                             |         |

| 21        |             |                              |      | 8255-PPI                                                                        | Regular                            | OHP,BB                             |         |

| 22        |             |                              |      | Modes of operation and interfacing to 8086                                      | Regular                            | BB                                 |         |

| 23 |    |    | Modes of operation and interfacing to 8086                                    | Regular    | BB        |

|----|----|----|-------------------------------------------------------------------------------|------------|-----------|

| 24 |    |    | Interfacing keyboard, display to 8086                                         | Regular    | OHP,BB    |

| 25 |    |    | Stepper motor interfacing to 8086                                             | Missing    | BB        |

| 26 |    |    | A/D converter interfacing to 8086                                             | Regular    | OHP,BB    |

| 27 |    |    | D/A converter interfacing to 8086                                             | Regular    | BB        |

| 28 |    |    | Tutorial class                                                                | Regular    | LCD,OHP,I |

| 29 |    |    | Memory interfacing to 8086                                                    | Regular    | OHP,BB    |

| 30 |    |    | Memory interfacing to 8086                                                    | Regular    | BB        |

| 32 |    |    | Interrupt structure of 8086,vector interrupt table, interrupt service routine | Regular    | OHP,BB    |

| 34 |    |    | Introduction to DOS and BIOS interrupts                                       | Missing    | BB        |

| 35 |    |    | Interrupt controller-8259, Interfacing DMA controller 8257 to 8086            | Additional | BB        |

| 36 |    |    | Tutorial class                                                                | Regular    | ОНРВВ     |

| 37 |    |    | 8251 USART architecture                                                       | Regular    | BB        |

|    |    |    | 8251 USART interfacing                                                        | Regular    | BB        |

| 38 |    |    | RS-232,IEEE 488 Standards                                                     | Missing    | OHP,BB    |

| 39 |    |    | Prototyping and troubleshooting                                               | Missing    | OHP,BB    |

| 40 |    |    | TTL to RS 232 and<br>RS-232 to TTL conversion                                 | Missing    | BB        |

| 41 | IV | 08 | Overview of 8051 microcontrollers                                             | Regular    | ОНР,ВВ    |

| 42 |    |    | Architecture of 8051microcontroller                                           | Regular    | BB        |

| 43 |    |    | I/O ports, memory segmentation of 8051                                        | Regular    | BB        |

| 44 |    |    | Addressing modes of 8051                                                      | Regular    | BB        |

| 45 |    |    | Instruction set of 8051                                                       | Regular    | BB        |

| 46 |    |    | Simple programs on 8051                                                       | Regular    | BB        |

| 47 |    |    | Simple programs on 8051                                                       | Regular    | ОНР,ВВ    |

| 49 |    |    | Tutorial class                                                                | Regular    | OHP,BB    |

| 50 | V  | 10 | Interrupts of 8051 microcontroller                                            | Regular    | OHP,BB    |

| 51 | Timer/counters of 8051                          | Regular | BB     |  |

|----|-------------------------------------------------|---------|--------|--|

| 52 | Serial communication of 8051                    | Regular | BB     |  |

| 53 | Programming timer interrupts                    | Regular | OHP,BB |  |

| 54 | Programming external hardware interrupts        | Regular | OHP,BB |  |

| 55 | Programming the serial communication interrupts | Regular | BB     |  |

| 56 | Programming 8051 timers/counters                | Regular | BB     |  |

# **ECE-B**

| SL.<br>No | Unit<br>No. | Total<br>No.o<br>Perio<br>ds | Topic to be covered in One lecture                                            | Regular/<br>Additional/<br>missing | Teaching<br>aids<br>LCD/OHP/<br>BB | Remarks |

|-----------|-------------|------------------------------|-------------------------------------------------------------------------------|------------------------------------|------------------------------------|---------|

| 1         | 1           | 11                           | Overview of basics from Switching The Logic Design and Computer Organization. | Additional                         | BB                                 |         |

| 2         |             |                              | Overview of MPMC syllabus and its importance in Real world                    | Additional                         | BB                                 |         |

| 3         |             |                              | Evolution of microprocessors and Introduction to 8085 microprocessor,         | Additional                         | OHP,BB                             |         |

| 4         |             | _                            | Architecture of 8086 Microprocessor – functional diagram description          | Regular                            | OHP,BB                             |         |

| 5         |             |                              | Register organization, memory segmentation                                    | Regular                            | OHP,BB                             |         |

| 6         |             |                              | Programming model, memory addresses                                           | Regular                            | OHP,BB                             |         |

| 7         |             |                              | Physical memory organization                                                  | Regular                            | BB                                 |         |

| 8         |             |                              | Signal description of 8086, Common function signals                           | Regular                            | BB                                 |         |

| 9         |             |                              | maximum and minimum mode signals                                              | Regular                            | BB                                 |         |

| 10        |             |                              | Timing diagrams, Interrupts of 8086                                           | Regular                            | OHP,BB                             |         |

| 11        |             |                              | Tutorial class                                                                | Regular                            | BB                                 |         |

| 12        | II          | 08                           | Instruction formats, addressing modes                                         | Regular                            | OHP,BB                             |         |

| 13        |             |                              | Instruction set of 8086                                                       | Regular                            | BB                                 |         |

| 14        |             |                              | Instruction set of 8086                                                       | Regular                            | BB                                 |         |

| 15 |     |    | Assembler directives, macros                                                    | Regular    | ОНР,ВВ    |

|----|-----|----|---------------------------------------------------------------------------------|------------|-----------|

| 16 |     |    | Simple programs on logical ,branch and call instructions                        | Regular    | BB        |

| 17 |     |    | Programs on sorting, string manipulations                                       | Regular    | BB        |

| 18 |     |    | Tutorial class                                                                  | Regular    | BB        |

| 19 |     |    | Introduction to Pentium and dual core processors                                | Additional | ОНР,ВВ    |

| 20 | III | 20 | Introduction to parallel data transfer methods and importance of port structure | Regular    | OHP,BB    |

| 21 |     |    | 8255-PPI                                                                        | Regular    | ОНР,ВВ    |

| 22 |     |    | Modes of operation and interfacing to 8086                                      | Regular    | BB        |

| 23 |     |    | Modes of operation and interfacing to 8086                                      | Regular    | BB        |

| 24 |     |    | Interfacing keyboard, display to 8086                                           | Regular    | ОНР,ВВ    |

| 25 |     |    | Stepper motor interfacing to 8086                                               | Missing    | BB        |

| 26 |     |    | A/D converter interfacing to 8086                                               | Regular    | OHP,BB    |

| 27 |     |    | D/A converter interfacing to 8086                                               | Regular    | BB        |

| 28 |     |    | Tutorial class                                                                  | Regular    | LCD,OHP,I |

| 29 |     |    | Memory interfacing to 8086                                                      | Regular    | ОНР,ВВ    |

| 30 |     |    | Memory interfacing to 8086                                                      | Regular    | BB        |

| 32 |     |    | Interrupt structure of 8086, vector interrupt table, interrupt service routine  | Regular    | ОНР,ВВ    |

| 34 |     |    | Introduction to DOS and BIOS interrupts                                         | Missing    | BB        |

| 35 |     |    | Interrupt controller-8259, Interfacing DMA controller 8257 to 8086              | Additional | BB        |

| 36 |     |    | Tutorial class                                                                  | Regular    | ОНРВВ     |

| 37 |     |    | 8251 USART architecture                                                         | Regular    | BB        |

|    |     |    | 8251 USART interfacing                                                          | Regular    | BB        |

| 38 |     |    | RS-232,IEEE 488 Standards                                                       | Missing    | ОНР,ВВ    |

| 39 |     |    | Prototyping and troubleshooting                                                 | Missing    | ОНР,ВВ    |

| 40 |     |    | TTL to RS 232 and<br>RS-232 to TTL conversion                                   | Missing    | BB        |

| 41 | IV  | 08 | Overview of 8051 microcontrollers                                               | Regular    | OHP,BB    |

| 42 |   |    | Architecture of 8051microcontroller             | Regular | BB     |

|----|---|----|-------------------------------------------------|---------|--------|

| 43 |   |    | I/O ports, memory segmentation of 8051          | Regular | BB     |

| 44 |   |    | Addressing modes of 8051                        | Regular | ВВ     |

| 45 |   |    | Instruction set of 8051                         | Regular | BB     |

| 46 |   |    | Simple programs on 8051                         | Regular | BB     |

| 47 |   |    | Simple programs on 8051                         | Regular | OHP,BB |

| 49 |   |    | Tutorial class                                  | Regular | OHP,BB |

| 50 | V | 10 | Interrupts of 8051 microcontroller              | Regular | OHP,BB |

| 51 |   |    | Timer/counters of 8051                          | Regular | BB     |

| 52 |   |    | Serial communication of 8051                    | Regular | BB     |

| 53 |   |    | Programming timer interrupts                    | Regular | OHP,BB |

| 54 |   |    | Programming external hardware interrupts        | Regular | ОНР,ВВ |

| 55 |   |    | Programming the serial communication interrupts | Regular | BB     |

| 56 |   |    | Programming 8051 timers/counters                | Regular | BB     |

# ECE-C

| SL.<br>No | Unit<br>No. | Total<br>No.o<br>Perio<br>ds | 2000 | Topic to be covered in One lecture                                            | Regular/<br>Additional/<br>missing | Teaching<br>aids<br>LCD/OHP/<br>BB | Remarks |

|-----------|-------------|------------------------------|------|-------------------------------------------------------------------------------|------------------------------------|------------------------------------|---------|

| 1         | 1           | 11                           |      | Overview of basics from Switching The Logic Design and Computer Organization. |                                    | BB                                 |         |

| 2         |             |                              |      | Overview of MPMC syllabus and its importance in Real world                    | Additional                         | BB                                 |         |

| 3         |             |                              |      | Evolution of microprocessors and Introduction to 8085 microprocessor,         | Additional                         | OHP,BB                             |         |

| 4         |             |                              |      | Architecture of 8086 Microprocessor – functional diagram description          | Regular                            | OHP,BB                             |         |

| 5         |             |                              |      | Register organization, memory segmentation                                    | Regular                            | OHP,BB                             |         |

| 6         |             |                              |      | Programming model, memory addresses                                           | Regular                            | OHP,BB                             |         |

| 7         |             |                              |      | Physical memory organization                                                  | Regular                            | BB                                 | _       |

| 8  |     |    | Signal description of 8086, Common                                              | Regular    | BB        |

|----|-----|----|---------------------------------------------------------------------------------|------------|-----------|

| 9  |     |    | function signals maximum and minimum mode signals                               | Regular    | BB        |

| 10 |     |    | Timing diagrams, Interrupts of 8086                                             | Regular    | ОНР,ВВ    |

| 11 |     |    | Tutorial class                                                                  | Regular    | BB        |

| 12 | II  | 08 | Instruction formats, addressing modes                                           | Regular    | ОНР,ВВ    |

|    |     | 00 | Instruction set of 8086                                                         |            |           |

| 13 |     |    |                                                                                 | Regular    | BB        |

| 14 |     |    | Instruction set of 8086                                                         | Regular    | BB        |

| 15 |     |    | Assembler directives, macros                                                    | Regular    | OHP,BB    |

| 16 |     |    | Simple programs on logical ,branch and call instructions                        | Regular    | BB        |

| 17 |     |    | Programs on sorting, string manipulations                                       | Regular    | BB        |

| 18 |     |    | Tutorial class                                                                  | Regular    | BB        |

| 19 |     |    | Introduction to Pentium and dual core processors                                | Additional | ОНР,ВВ    |

| 20 | III | 20 | Introduction to parallel data transfer methods and importance of port structure | Regular    | ОНР,ВВ    |

| 21 |     |    | 8255-PPI                                                                        | Regular    | ОНР,ВВ    |

| 22 |     |    | Modes of operation and interfacing to 8086                                      | Regular    | BB        |

| 23 |     |    | Modes of operation and interfacing to 8086                                      | Regular    | BB        |

| 24 |     |    | Interfacing keyboard, display to 8086                                           | Regular    | OHP,BB    |

| 25 |     |    | Stepper motor interfacing to 8086                                               | Missing    | BB        |

| 26 |     |    | A/D converter interfacing to 8086                                               | Regular    | ОНР,ВВ    |

| 27 |     |    | D/A converter interfacing to 8086                                               | Regular    | BB        |

| 28 |     |    | Tutorial class                                                                  | Regular    | LCD,OHP,I |

| 29 |     |    | Memory interfacing to 8086                                                      | Regular    | ОНР,ВВ    |

| 30 |     |    | Memory interfacing to 8086                                                      | Regular    | BB        |

| 32 |     |    | Interrupt structure of 8086, vector interrupt table, interrupt service routine  | Regular    | ОНР,ВВ    |

| 34 |     |    | Introduction to DOS and BIOS interrupts                                         | Missing    | BB        |

| 35 |     |    | Interrupt controller-8259, Interfacing DMA controller 8257 to 8086              | Additional | BB        |

| 36 |    |    | Tutorial class                                  | Regular | ОНРВВ  |

|----|----|----|-------------------------------------------------|---------|--------|

| 37 |    |    | 8251 USART architecture                         | Regular | BB     |

|    |    |    | 8251 USART interfacing                          | Regular | BB     |

| 38 |    |    | RS-232,IEEE 488 Standards                       | Missing | OHP,BB |

| 39 |    |    | Prototyping and troubleshooting                 | Missing | OHP,BB |

| 40 |    |    | TTL to RS 232 and<br>RS-232 to TTL conversion   | Missing | BB     |

| 41 | IV | 08 | Overview of 8051 microcontrollers               | Regular | OHP,BB |

| 42 |    |    | Architecture of 8051microcontroller             | Regular | BB     |

| 43 |    |    | I/O ports, memory segmentation of 8051          | Regular | BB     |

| 44 |    |    | Addressing modes of 8051                        | Regular | BB     |

| 45 |    |    | Instruction set of 8051                         | Regular | BB     |

| 46 |    |    | Simple programs on 8051                         | Regular | BB     |

| 47 |    |    | Simple programs on 8051                         | Regular | OHP,BB |

| 49 |    |    | Tutorial class                                  | Regular | OHP,BB |

| 50 | V  | 10 | Interrupts of 8051 microcontroller              | Regular | OHP,BB |

| 51 |    |    | Timer/counters of 8051                          | Regular | BB     |

| 52 |    |    | Serial communication of 8051                    | Regular | BB     |

| 53 |    |    | Programming timer interrupts                    | Regular | OHP,BB |

| 54 |    |    | Programming external hardware interrupts        | Regular | OHP,BB |

| 55 |    |    | Programming the serial communication interrupts | Regular | BB     |

| 56 |    |    | Programming 8051 timers/counters                | Regular | BB     |

# ECE -D

| SL. | Unit | Total | Date | Topic to be covered in One lecture | Regular/    | Teaching | Remarks |

|-----|------|-------|------|------------------------------------|-------------|----------|---------|

| No  | No.  | No.o  |      |                                    | Additional/ | aids     |         |

|    |     | Perio<br>ds |                                                                                 | missing    | LCD/OHP/<br>BB |

|----|-----|-------------|---------------------------------------------------------------------------------|------------|----------------|

| 1  | 1   | 11          | Overview of basics from Switching The Logic Design and Computer Organization.   | Additional | BB             |

| 2  |     |             | Overview of MPMC syllabus and its importance in Real world                      | Additional | BB             |

| 3  |     |             | Evolution of microprocessors and Introduction to 8085 microprocessor,           | Additional | OHP,BB         |

| 4  |     |             | Architecture of 8086 Microprocessor – functional diagram description            | Regular    | OHP,BB         |

| 5  |     |             | Register organization, memory segmentation                                      | Regular    | OHP,BB         |

| 6  |     |             | Programming model, memory addresses                                             | Regular    | OHP,BB         |

| 7  |     |             | Physical memory organization                                                    | Regular    | BB             |

| 8  |     |             | Signal description of 8086, Common function signals                             | Regular    | BB             |

| 9  |     |             | maximum and minimum mode signals                                                | Regular    | BB             |

| 10 |     |             | Timing diagrams, Interrupts of 8086                                             | Regular    | ОНР,ВВ         |

| 11 |     |             | Tutorial class                                                                  | Regular    | BB             |

| 12 | II  | 08          | Instruction formats, addressing modes                                           | Regular    | ОНР,ВВ         |

| 13 |     |             | Instruction set of 8086                                                         | Regular    | BB             |

| 14 |     |             | Instruction set of 8086                                                         | Regular    | BB             |

| 15 |     |             | Assembler directives, macros                                                    | Regular    | ОНР,ВВ         |

| 16 |     |             | Simple programs on logical ,branch and call instructions                        | Regular    | BB             |

| 17 |     |             | Programs on sorting, string manipulations                                       | Regular    | BB             |

| 18 |     |             | Tutorial class                                                                  | Regular    | ВВ             |

| 19 |     |             | Introduction to Pentium and dual core processors                                | Additional | ОНР,ВВ         |

| 20 | III | 20          | Introduction to parallel data transfer methods and importance of port structure | Regular    | ОНР,ВВ         |

| 21 |     |             | 8255-PPI                                                                        | Regular    | ОНР,ВВ         |

| 22 |     |             | Modes of operation and interfacing to 8086                                      | Regular    | BB             |

| 23 |     |             | Modes of operation and interfacing to 8086                                      | Regular    | ВВ             |

| 24 |     |             | Interfacing keyboard, display to 8086                                           | Regular    | ОНР,ВВ         |

| 25 |     |             | Stepper motor interfacing to 8086                                               | Missing    | BB             |

| 26 |    |    | A/D converter interfacing to 8086             | Regular    | OHP,BB    |

|----|----|----|-----------------------------------------------|------------|-----------|

| 27 |    |    | D/A converter interfacing to 8086             | Regular    | BB        |

| 28 |    |    | Tutorial class                                | Regular    | LCD,OHP,I |

| 29 |    |    | Memory interfacing to 8086                    | Regular    | OHP,BB    |

| 30 |    |    | Memory interfacing to 8086                    | Regular    | BB        |

| 32 |    |    | Interrupt structure of 8086, vector interrupt | Regular    | OHP,BB    |

| 34 |    |    | Introduction to DOS and BIOS interrupts       | Missing    | ВВ        |

| 35 |    |    | Interrupt controller-8259, Interfacing        | Additional | BB        |

| 36 |    |    | DMA controller 8257 to 8086  Tutorial class   | Regular    | ОНРВВ     |

| 37 |    |    | 8251 USART architecture                       | Regular    | BB        |

|    |    |    | 8251 USART interfacing                        | Regular    | BB        |

| 38 |    |    | RS-232,IEEE 488 Standards                     | Missing    | ОНР,ВВ    |

| 39 |    |    | Prototyping and troubleshooting               | Missing    | ОНР,ВВ    |

| 40 |    |    | TTL to RS 232 and<br>RS-232 to TTL conversion | Missing    | BB        |

| 41 | IV | 08 | Overview of 8051 microcontrollers             | Regular    | OHP,BB    |

| 42 |    |    | Architecture of 8051microcontroller           | Regular    | BB        |

| 43 |    |    | I/O ports, memory segmentation of 8051        | Regular    | BB        |

| 44 |    |    | Addressing modes of 8051                      | Regular    | BB        |

| 45 |    |    | Instruction set of 8051                       | Regular    | BB        |

| 46 |    |    | Simple programs on 8051                       | Regular    | BB        |

| 47 |    |    | Simple programs on 8051                       | Regular    | OHP,BB    |

| 49 |    |    | Tutorial class                                | Regular    | OHP,BB    |

| 50 | V  | 10 | Interrupts of 8051 microcontroller            | Regular    | OHP,BB    |

| 51 |    |    | Timer/counters of 8051                        | Regular    | BB        |

| 52 |    |    | Serial communication of 8051                  | Regular    | BB        |

| 53 |    |    | Programming timer interrupts                  | Regular    | ОНР,ВВ    |

| 54 |  | Programming external hardware interrupts        | Regular | OHP,BB |  |

|----|--|-------------------------------------------------|---------|--------|--|

| 55 |  | Programming the serial communication interrupts | Regular | BB     |  |

| 56 |  | Programming 8051 timers/counters                | Regular | BB     |  |

# 14.Detailed notes

# **UNIT-I**

# **8085 Microprocessor** *Contents*

- •General definitions

- •Overview of 8085 microprocessor

- •Overview of 8086 microprocessor

- •Signals and pins of 8086 microprocessor

# The salient features of 8085 µp are:

- •It is a 8 bit microprocessor.

- •It is manufactured with N-MOS technology.

- •It has 16-bit address bus and hence can address up to 216 =65536 bytes (64KB) memory locations through  $A_0$ - $A_{15}$ .

- •The first 8 lines of address bus and 8 lines of data bus are multiplexed AD0 AD7.

- •Data bus is a group of 8 lines D0 D7.

- •It supports external interrupt request.

- •A 16 bit program counter (PC)

- •A 16 bit stack pointer (SP)

- •Six 8-bit general purpose register arranged in pairs: BC, DE, HL.

- •It requires a signal +5V power supply and operates at 3.2 MHZ single phase clock.

- •It is enclosed with 40 pins DIP (Dual in line package).

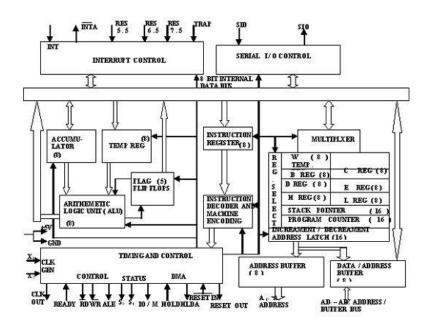

# Overview of 8085 microprocessor

8085 Architecture

- Pin Diagram

- Functional Block Diagram

# **Instruction Set**

8085 instruction set consists of the following instructions:

- Data moving instructions.

- Arithmetic add, subtract, increment and decrement.

- Logic AND, OR, XOR and rotate.

- Control transfer conditional, unconditional, call subroutine, return from subroutine and restarts.

- Input/Output instructions.

- Other setting/clearing flag bits, enabling/disabling interrupts, stack operations, etc.

# Addressing mode

•Register - references the data in a register or in a register pair.

**Register indirect** - instruction specifies register pair containing address, where the data is located.

**Direct, Immediate** - 8 or 16-bit data.

Advantages of 8086 over 8085 are:

- 1. pipelining is employed making the execution faster.

- 2. data bus width increased to 16 bits.

- 3. higher memory of 1MB.

- 4. some instructions such as MUL or DIV are available for multiplication and division.

- 5. increased instruction set making the programming easier.

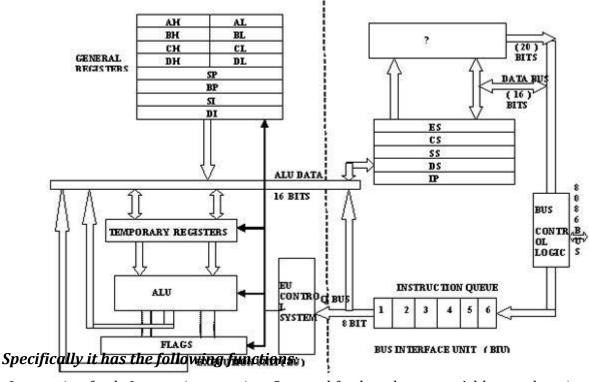

- •EU executes instructions from the instruction system byte queue.

- •Both units operate asynchronously to give the 8086 an overlapping instruction fetch and execution mechanism which is called as Pipelining. This results in efficient use of the system bus and system performance.

- •BIU contains Instruction queue, Segment registers, Instruction pointer, Address adder.

- •EU contains Control circuitry, Instruction decoder, ALU, Pointer and Index register, Flag register.

### **BUS INTERFACR UNIT:**

- It provides a full 16 bit bidirectional data bus and 20 bit address bus.

- •The bus interface unit is responsible for performing all external bus operations.

- •Instruction fetch, Instruction queuing, Operand fetch and storage, Address relocation and Bus control.

- •The BIU uses a mechanism known as an instruction stream queue to implement a *pipeline architecture.*

- •This queue permits prefetch of up to six bytes of instruction code. When ever the queue of the BIU is not full, it has room for at least two more bytes and at the same time the EU is not requesting it to read or write operands from memory, the BIU is free to look ahead in the program by prefetching the next sequential instruction.

- •These prefetching instructions are held in its FIFO queue. With its 16 bit data bus, the BIU fetches two instruction bytes in a single memory cycle.

- •After a byte is loaded at the input end of the queue, it automatically shifts up through the FIFO to the empty location nearest the output.

- •The EU accesses the queue from the output end. It reads one instruction byte after the other from the output of the queue. If the queue is full and the EU is not requesting access to operand in memory.

- •These intervals of no bus activity, which may occur between bus cycles are known as *Idle state*.

- •If the BIU is already in the process of fetching an instruction when the EU request it to read or write operands from memory or I/O, the BIU first completes the instruction fetch bus cycle before initiating the operand read / write cycle.

- •The BIU also contains a dedicated adder which is used to generate the 20bit physical address that is output on the address bus. This address is formed med by combining the current contents of the code segment CS register and the current contents of the instruction pointer IP register.

- •The BIU is also responsible for generating bus control signals such as those for memory read or write and I/O read or write.

### **EXECUTION UNIT**

The Execution unit is responsible for decoding and executing all instructions.

- •The EU extracts instructions from the top of the queue in the BIU, decodes them, generates operands if necessary, passes them to the BIU and requests it to perform the read or write bys cycles to memory or I/O and perform the operation specified by the instruction on the operands.

- •During the execution of the instruction, the EU tests the status and control flags and updates them based on the results of executing the instruction.

- •If the queue is empty, the EU waits for the next instruction byte to be fetched and shifted to top of the queue.

- •When the EU executes a branch or jump instruction, it transfers control to a location

corresponding to another set of sequential instructions.

## SPECIAL FUNCTIONS OF GENERAL PURPOSE REGISTERS

**Accumulator** register consists of 2 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX. AL in this case contains the low-order byte of the word, and AH contains the high-order byte. Accumulator can be used for I/O operations and string manipulation.

**Base** register consists of 2 8-bit registers BL and BH, which can be combined together and used as a 16-bit register BX. BL in this case contains the low-order byte of the word, and BH contains the high-order byte. BX register usually contains a data pointer used for based, based indexed or register indirect addressing.

**Count** register consists of 2 8-bit registers CL and CH, which can be combined together and used as a 16-bit register CX. When combined, CL register contains the low-order byte of the word, and CH contains the high-order byte. Count register can be used as a counter in string manipulation and shift/rotate instructions.

**Data** register consists of 2 8-bit registers DL and DH, which can be combined together and used as a 16-bit register DX. When combined, DL register contains the low-order byte of the word, and DH contains the high-order byte. Data register can be used as a port number in I/O operations. In integer 32-bit multiply and divide instruction the DX register contains high-order word of the initial or resulting number.

### **SPECIAL FUNCTIONS OF SPECIAL PURPOSE REGISTERS**

**Stack Pointer** (SP) is a 16-bit register pointing to program stack.

**Base Pointer** (BP) is a 16-bit register pointing to data in stack segment. BP register is usually used for based, based indexed or register indirect addressing.

**Source Index** (SI) is a 16-bit register. SI is used for indexed, based indexed and register indirect addressing, as well as a source data address in string manipulation instructions.

**Destination Index** (DI) is a 16-bit register. DI is used for indexed, based indexed and register indirect addressing, as well as a destination data address in string manipulation instructions. The si and di registers (Source Index and Destination Index ) have some special purposes as well. You may use these registers as pointers (much like the bx register) to indirectly access memory. You'll also use these registers with the 8086 string instructions when processing character strings.

The bp register (Base Pointer) is similar to the bx register. You'll generally use this register to access parameters and local variables in a procedure.

The sp register (Stack Pointer) has a very special purpose - it maintains the program stack. Normally, you would not use this register for arithmetic computations. The proper operation of most programs depends upon the careful use of this register.

### **SEGMENTATION:**

Since address registers and address operands are only 16 bits they can only address 64k bytes. In order toaddress the 20-bit address range of the 8086, physical addresses (those that are put on the address bus) are always formed by adding the values of one of the instruction is executed? The use of segment registers reduces the size of pointers to 16 bits.

This reduces the code size but also restricts the addressing range of a pointer to 64k bytes. Performing address arithmetic within data structures larger than 64k is awkward. This is the biggest drawback of the 8086 architecture. We will restrict oursives to short programs where all of the code, data and stack are placed into thesame 64k segment (i.e. CS=DS=SS).

Most of the registers contain data/instruction offsets within 64 KB memory segment. There are four different 64 KB segments for instructions, stack, data and extra data. To specify where in 1 MB of processor memory these 4 segments are located the processor uses four segment registers:

# **Memory**

- •Program, data and stack memories occupy the same memory space. As the most of the processor instructions use 16-bit pointers the processor can effectively address only 64 KB of memory.

- To access memory outside of 64 KB the CPU uses special segment registers to specify where the code, stack and data 64 KB segments are positioned within 1 MB of memory (see the "Registers" section below).

- •16-bit pointers and data are stored as:

address: low-order byte

address+1: high-order byte

•Program memory - program can be located anywhere in memory. Jump and call instructions can be used for short jumps within currently selected 64 KB code segment, as well as for far jumps anywhere within 1 MB of memory.

- •All conditional jump instructions can be used to jump within approximately +127 to -127 bytes from current instruction.

- •Data memory the processor can access data in any one out of 4 available segments, which limits the size of accessible memory to 256 KB (if all four segments point to different 64 KB blocks).

- •Accessing data from the Data, Code, Stack or Extra segments can be usually done by prefixing instructions with the DS:, CS:, SS: or ES: (some registers and instructions by default may use the ES or SS segments instead of DS segment).

- •Word data can be located at odd or even byte boundaries. The processor uses two memory accesses to read 16-bit word located at odd byte boundaries. Reading word data from even byte boundaries requires only one memory access.

- •Stack memory can be placed anywhere in memory. The stack can be located at odd memory addresses, but it is not recommended for performance reasons (see "Data Memory" above).

### **Reserved locations:**

- •0000h 03FFh are reserved for interrupt vectors. Each interrupt vector is a 32-bit pointer in format segment: offset.

- •FFFF0h FFFFFh after RESET the processor always starts program execution at the FFFF0h address.

*segment registers* to the 16-bit address to form a 20-bit address.

The segment registers themselves only contain themost-significant 16 bits of the 20-bit value that is contributed by the segment registers. The least significant four bits of these gment address are always zero.

By default, the DS (data segment) is used fordata transfer instructions (e.g. MOV), CS(codesegment) is used with control transfer instructions(e.g. JMP or CALL), and SS is used with the stackpointer (e.g. PUSH or to save/restore addresses duringCALL/RET or INT instructions).

Exercise: If DS contains 0100H, what address will be written by the instruction MOV [2000H],AL? If CX contains 1122H, SP contains 1234H, and SS contains 2000H, what memory values will change and what will be their values when the PUSH CX

**Code segment** (CS) is a 16-bit register containing address of 64 KB segment with processor instructions. The processor uses CS segment for all accesses to instructions referenced by instruction pointer (IP) register. CS register cannot be changed directly.

The CS register is automatically updated during far jump, far call and far return instructions.

**Stack segment** (SS) is a 16-bit register containing address of 64KB segment with program stack. By default, the processor assumes that all data referenced by the stack pointer (SP) and base pointer (BP) registers is located in the stack segment. SS register can be changed directly using POP instruction.

**Data segment** (DS) is a 16-bit register containing address of 64KB segment with program data. By default, the processor assumes that all data referenced by general registers (AX, BX, CX, DX) and index register (SI, DI) is located in the data segment. DS register can be changed directly using POP and LDS instructions.

**Extra segment** (ES) is a 16-bit register containing address of 64KB segment, usually with program data. By default, the processor assumes that the DI register references the ES segment in string manipulation instructions. ES register can be changed directly using POP and LES instructions.

It is possible to change default segments used by general and index registers by prefixing instructions with a CS, SS, DS or ES prefix.

# **8086 FLAG REGISTER**

**Flags** is a 16-bit register containing 9 1-bit flags:

- Overflow Flag (OF) set if the result is too large positive number, or is too small negative number to fit into destination operand.

- Direction Flag (DF) if set then string manipulation instructions will autodecrement index registers. If cleared then the index registers will be autoincremented.

- Interrupt-enable Flag (IF) setting this bit enables maskable interrupts.

- Single-step Flag (TF) if set then single-step interrupt will occur after the next instruction.

- Sign Flag (SF) set if the most significant bit of the result is set.

- Zero Flag (ZF) set if the result is zero.

- Auxiliary carry Flag (AF) set if there was a carry from or borrow to bits 0-3 in the AL register.

- Parity Flag (PF) set if parity (the number of "1" bits) in the low-order byte of the result is even.

Carry Flag (CF) - set if there was a carry from or borrow to the most significant bit during last result calculation

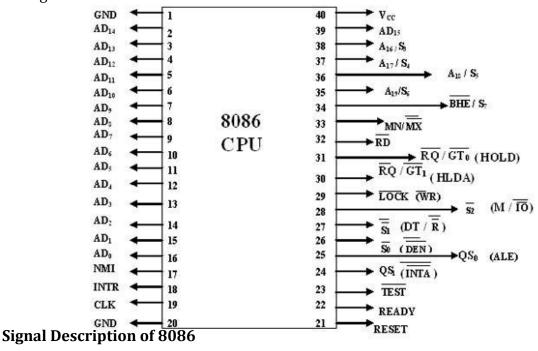

The Microprocessor 8086 is a 16-bit CPU available in different clock rates and packaged in a 40 pin CERDIP or plastic package.

- •The 8086 operates in single processor or multiprocessor configuration to achieve high performance. The pins serve a particular function in minimum mode (single processor mode) and other function in maximum mode configuration (multiprocessor mode).

- •The 8086 signals can be categorized in three groups. The first are the signal having common functions in minimum as well as maximum mode

- •The second are the signals which have special functions for minimum mode and third are the signals having special functions for maximum mode.

# The following signal descriptions are common for both modes.

**AD15-AD0**: These are the time multiplexed memory I/O address and data lines.

- Address remains on the lines during T1 state, while the data is available on the data bus during T2, T3, Tw and T4.

- These lines are active high and float to a tristate during interrupt acknowledge and local bus hold acknowledge cycles

A19/S6,A18/S5,A17/S4,A16/S3: These are the time multiplexed address and status lines.

• During T1 these are the most significant address lines for memory operations.

- •During I/O operations, these lines are low. During memory or I/O operations, status information is available on those lines for T2,T3,Tw and T4.

- The status of the interrupt enable flag bit is updated at the beginning of each clock cycle.

- •The S4 and S3 combinedly indicate which segment register is presently being used for memory accesses as in below fig.

- •These lines float to tri-state off during the local bus hold acknowledge. The status line S6 is always low .

- •The address bit are separated from the status bit using latches controlled by the ALE signal.