# **Courset file contents:**

| S.No | Name of the Topic                                                               | Page No |

|------|---------------------------------------------------------------------------------|---------|

| 1.   | Cover page                                                                      |         |

| 2.   | Syllabus copy                                                                   |         |

| 3.   | Vision of the department                                                        |         |

| 4.   | Mission of the department                                                       |         |

| 5.   | PEO's and PO's                                                                  |         |

| 6.   | Course objectives and outcomes                                                  |         |

| 7.   | Brief notes on the importance of the course and how it fits into the curriculum |         |

| 8.   | Prerequisites if any                                                            |         |

| 9.   | Instructional Learning Outcomes                                                 |         |

| 10.  | Course mapping with Pos                                                         |         |

| 11.  | Class Time table                                                                |         |

| 12.  | Individual time table                                                           |         |

| 13.  | Lecture schedule with methodology being used/adopted                            |         |

| 14.  | Detailed notes                                                                  |         |

| 15.  | Additional topics                                                               |         |

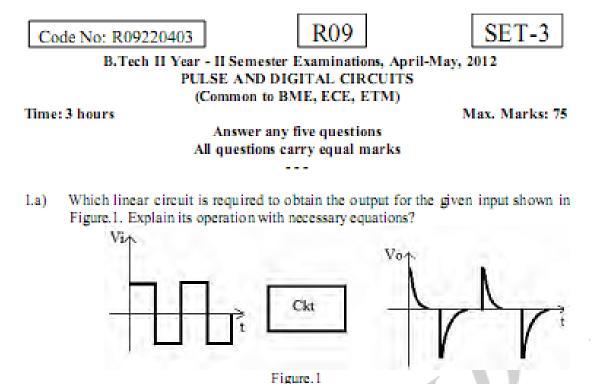

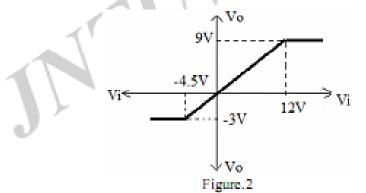

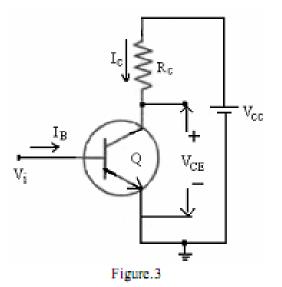

| 16.  | University Question papers of previous years                                    |         |

| 17.  | Question Bank                                                                   |         |

| 18.  | Assignment topics                                                               |         |

| 19.  | Unit-wise quiz questions and long answer questions                              |         |

| 20.  | Tutorial problems                                                               |         |

| 21.  | Known gaps, if any inclusion of the same in lecture schedule                    |         |

| 22.  | Discussion topics, if any                                                       |         |

| 23.  | References, Journals, websites and E-links if any                               |         |

| 24.  | Quality Control Sheets                                                          |         |

|      | a. Course end survey                                                            |         |

|      | b. Teaching Evaluation                                                          |         |

| 25.  | Students List                                                                   |         |

| 26.  | Group-Wise students list for discussion topics                                  |         |

| <u>Geethanjali College</u>                    | of Engineering and Technology |

|-----------------------------------------------|-------------------------------|

| DEPARTMENT OF ELF                             | ECTRONICS & COMMUNICATIONS    |

| (Name of the Subject/Lab Course) : Pulse &    | z Digital Circuits            |

| ( <b>JNTU CODE: A40415</b> )                  | Programme : UG                |

| Branch: ECE                                   | Version No : 4                |

| Year: II                                      | Document Number : GCET/ECE/   |

| Semester: II                                  | No. of Pages :                |

| Classification status (Unrestricted/Restricte | d): Unrestricted              |

| Distribution List:                            |                               |

| Prepared by :                                 | Updated by :                  |

| 1) Name : M.Muthamma                          | 1) Name :                     |

| 2) Sign :                                     | 2) Sign :                     |

| 3) Design : Assistant Professor               | 3) Design :                   |

| 4) Date : 24/ 12/ 2014                        | 4) Date :                     |

|                                               |                               |

| Verified by :*For Q.C only                    |                               |

| 1) Name :                                     | 1)Name :                      |

| 2) Sign :                                     | 2) Sign :                     |

| 3) Design :                                   | 3) Design :                   |

| 4) Date :                                     | 4) Date :                     |

| Approved by (HOD) :                           |                               |

| 1) Name :                                     |                               |

| 2) Sign :                                     |                               |

| 3) Date :                                     |                               |

#### 2. Syllabus copy

#### JAWAHARLAL NEHRU TECHNOLOGIVAL

#### UNIVERSITY HYDERABAD

**Objective:**

II Year B.Tech. ECE -II Sem

T PC

4+1\*04

Pulse and Digital Circuits (PDC)

#### <u>UNIT I</u>

#### LINEAR WAVE SHAPING

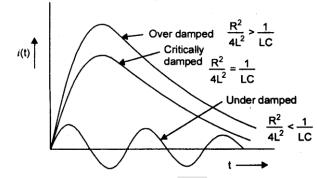

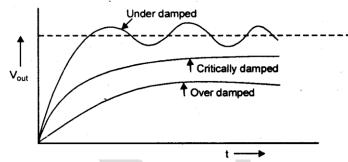

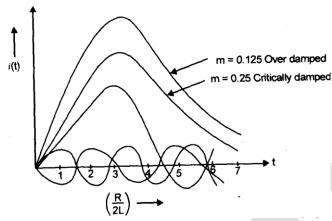

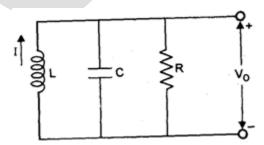

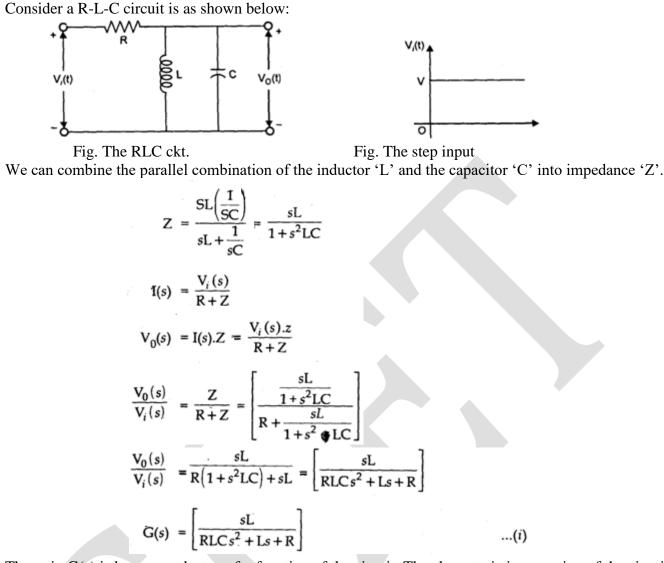

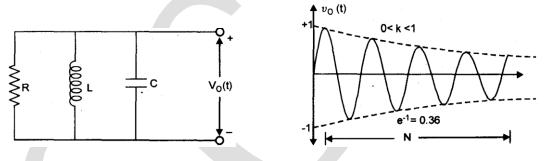

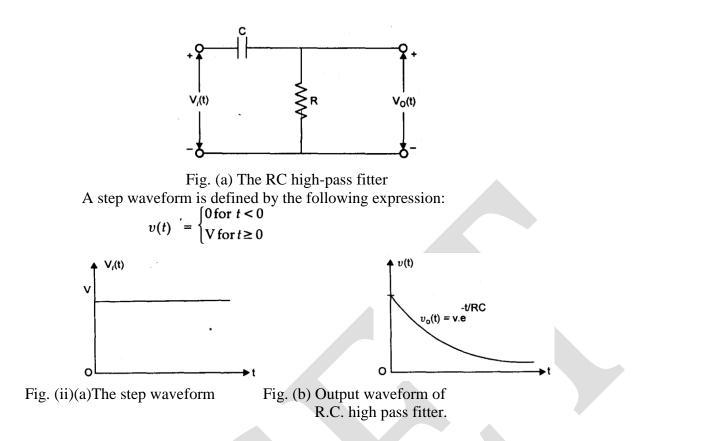

High pass and low pass RC circuits and their response for sinusoidal, step, pulse, square and ramp inputs. High pass RC network as differentiator, Low pass RC network as an integrator, Attenuators and its application as a CRO probe, RL and RLC circuits and their response for step input, Ringing circuit.

#### <u>UNIT II</u>

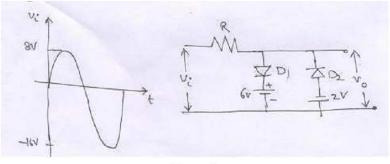

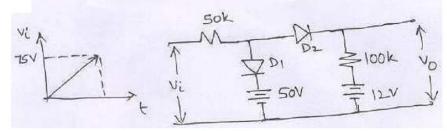

#### NON-LINEAR WAVE SHAPING

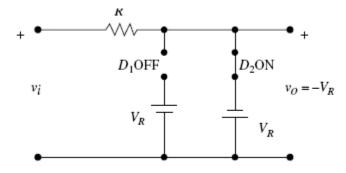

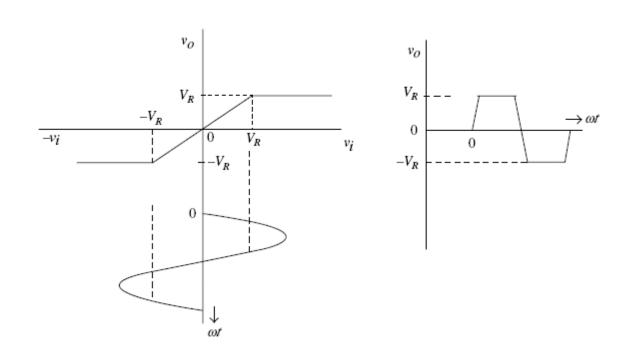

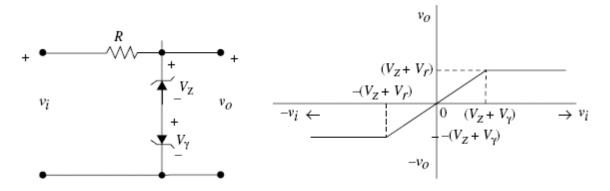

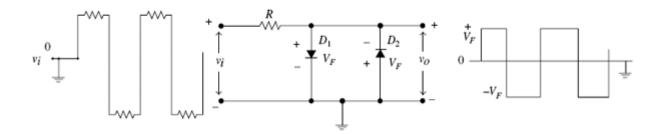

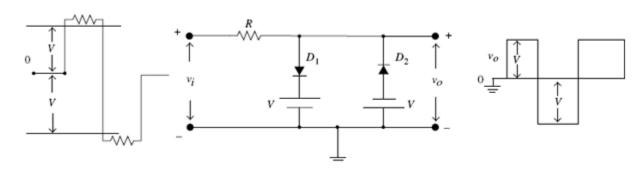

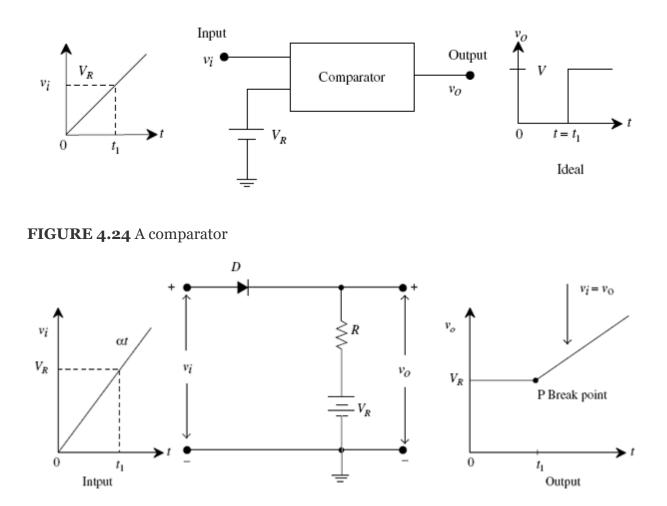

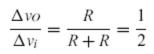

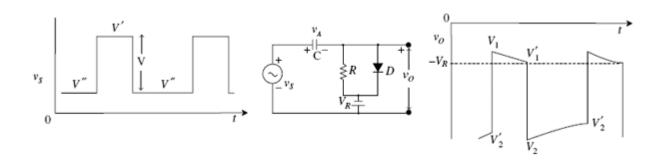

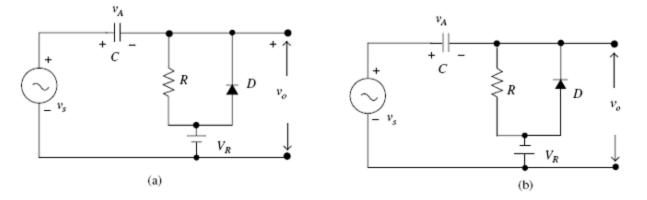

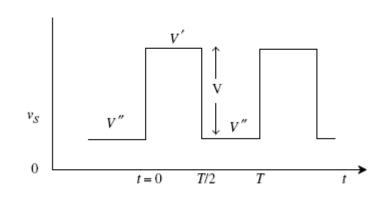

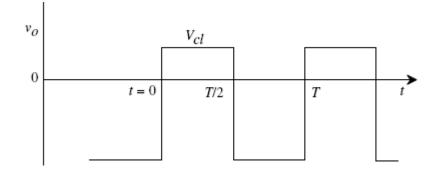

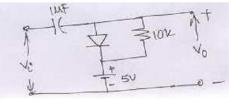

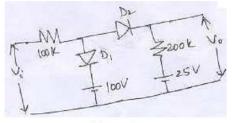

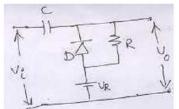

Diode clippers, Transistor clippers, clipping at two independent levels, Comparators, Applications of Voltage Comparators, Clamping operation, Clamping circuit taking Source and Diode resistance into account, Clamping circuit theorem, Practical clamping circuits, Effect of diode characteristics on clamping Voltage, Synchronized Clamping.

#### <u>UNITIII</u>

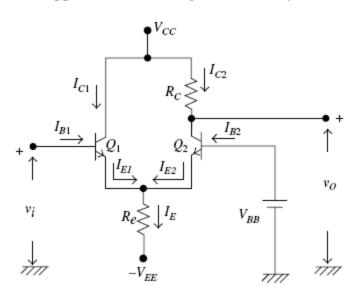

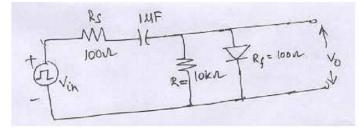

#### SWITCHING CHARACTERISTICS OF DEVICES

Diode as a switch, Piecewise linear diode characteristics, Diode Switching times, Transistor as a Switch, Break down voltages, Transistor in saturation, Temperature variation of saturation parameters, Transistor-switching times, Silicon Controlled switch circuits.

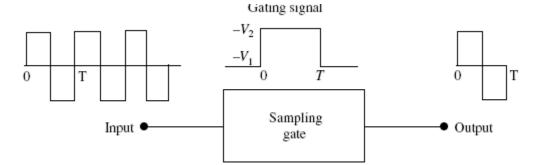

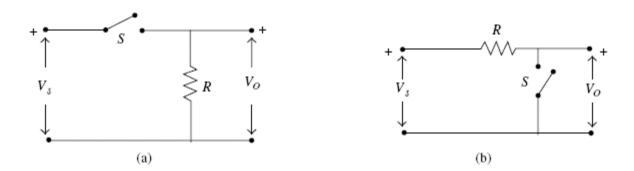

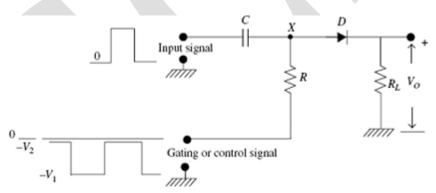

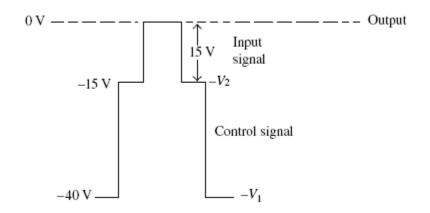

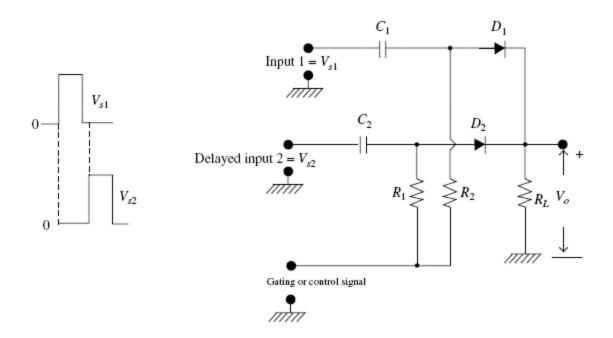

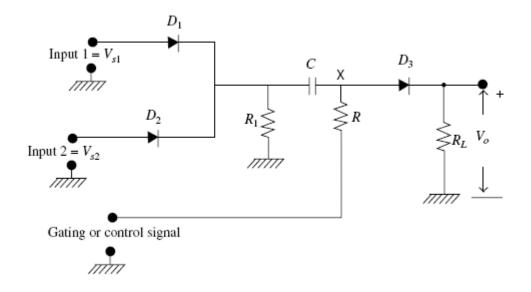

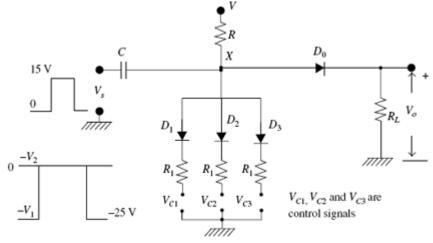

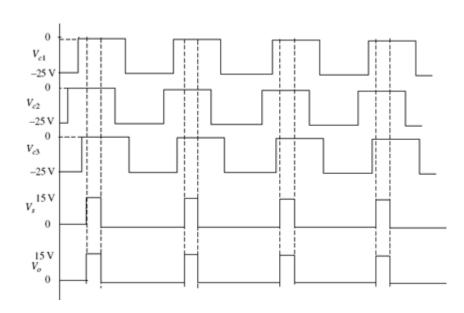

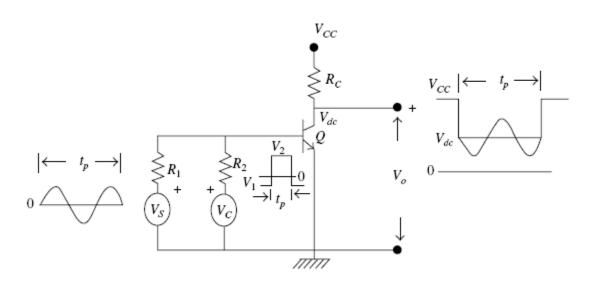

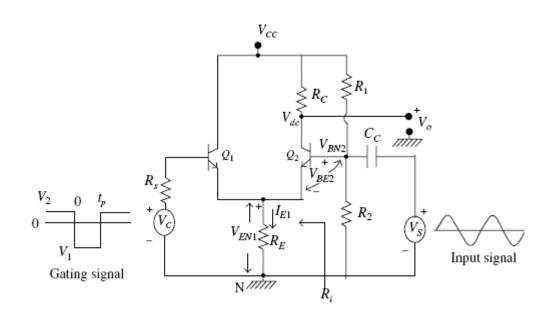

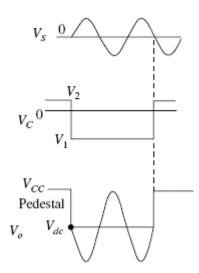

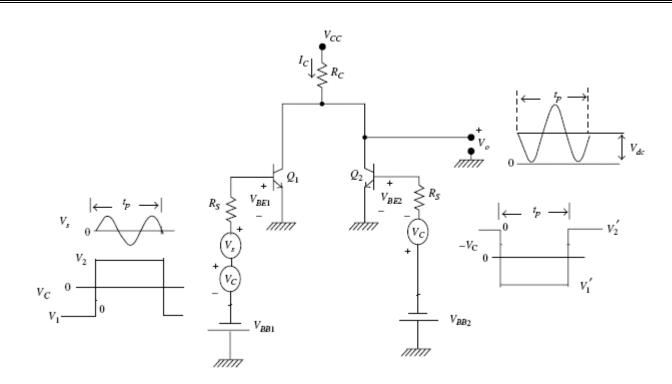

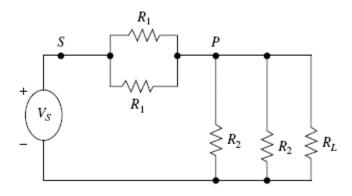

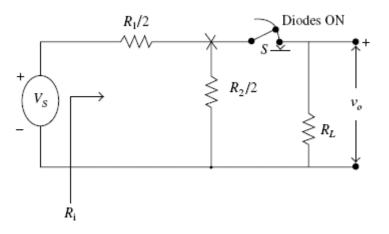

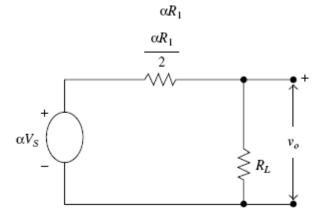

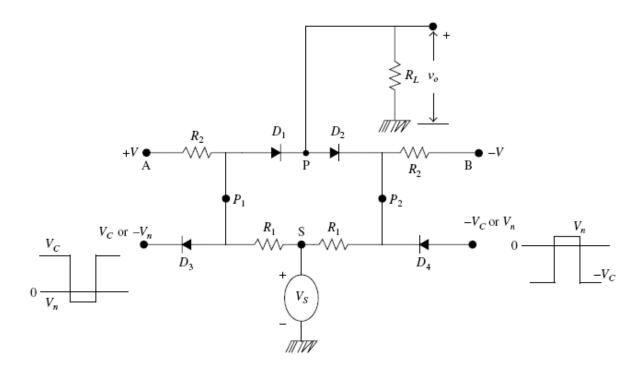

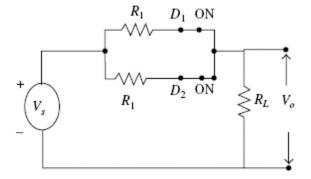

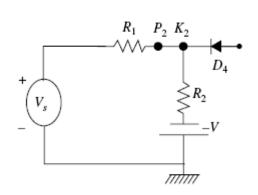

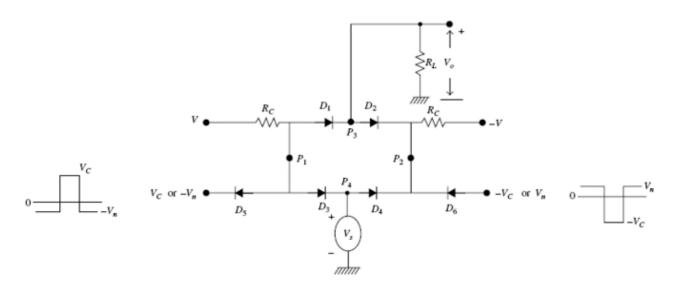

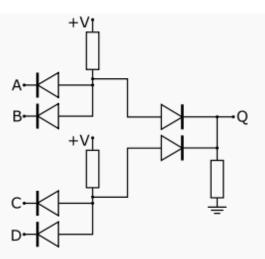

#### SAMPLING GATES

Basic operating principles of sampling gates, Unidirectional and Bi-directional sampling gates, Four Diode Sampling Gate, Reduction of pedestal in Gate Circuits, Six Diode Gate, Applications of sampling gates.

#### <u>UNIT IV</u>

#### **MULTIVIBRATORS**

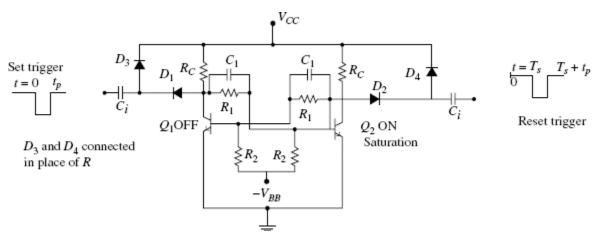

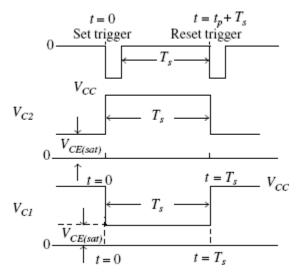

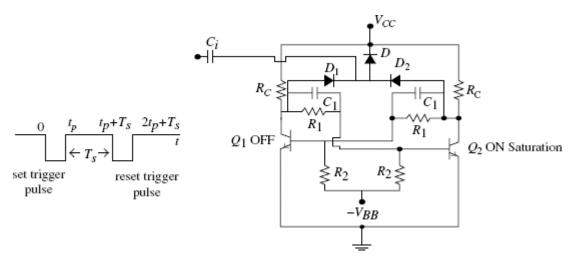

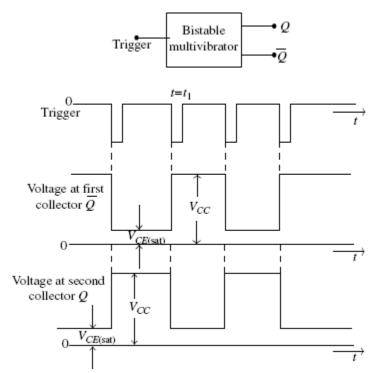

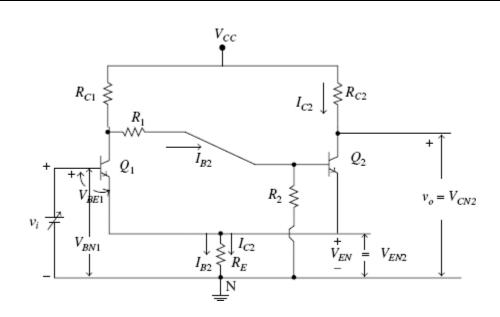

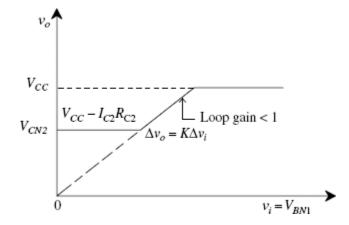

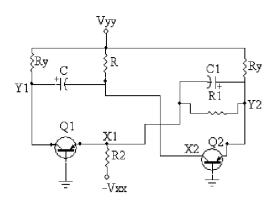

Analysis and Design of Bistable, Monostable, Astable Multivibrators and Schmitt trigger using transistors.

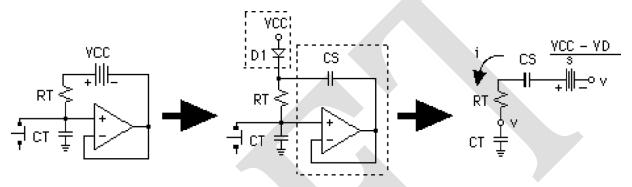

#### TIME BASE GENERATORS

General features of a time base signal, methods of generating time base waveform, Miller and Bootstrap time base generators – Basic Principles, Transistor Miller Time Base Generator, Transistor Bootstrap Time Base Generator, Current Time Base Generators, Methods of Linearity improvement.

#### UNIT V

#### SYNCHRONIZATION AND FREQUENCY DIVISION

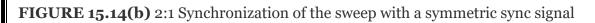

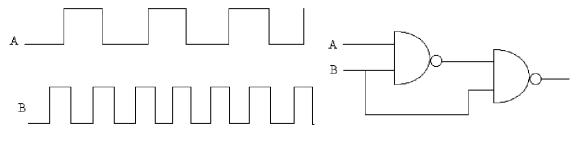

Pulse Synchronization of Relaxation Devices, Frequency division in Sweep Circuit, Stability of Relaxation devices, Astable Relaxation circuits, Monost Transistors able relaxation circuits, Synchronization of a sweep circuit with symmetrical signals, Sine wave frequency division with a sweep circuit, A Sinusoidal Divider using Regeneration and Modulation *REALIZATION OF LOGIC GATES USING DIODES & TRANSISTORS*

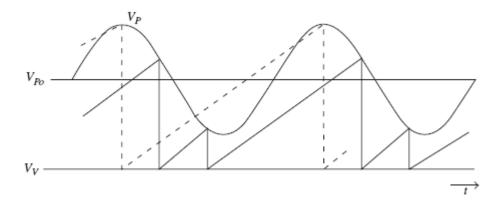

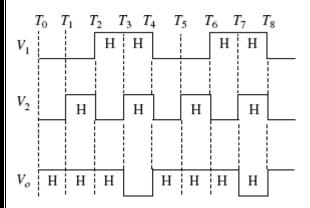

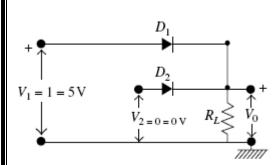

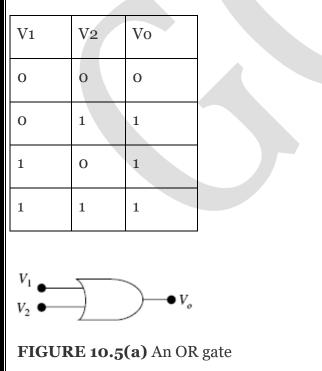

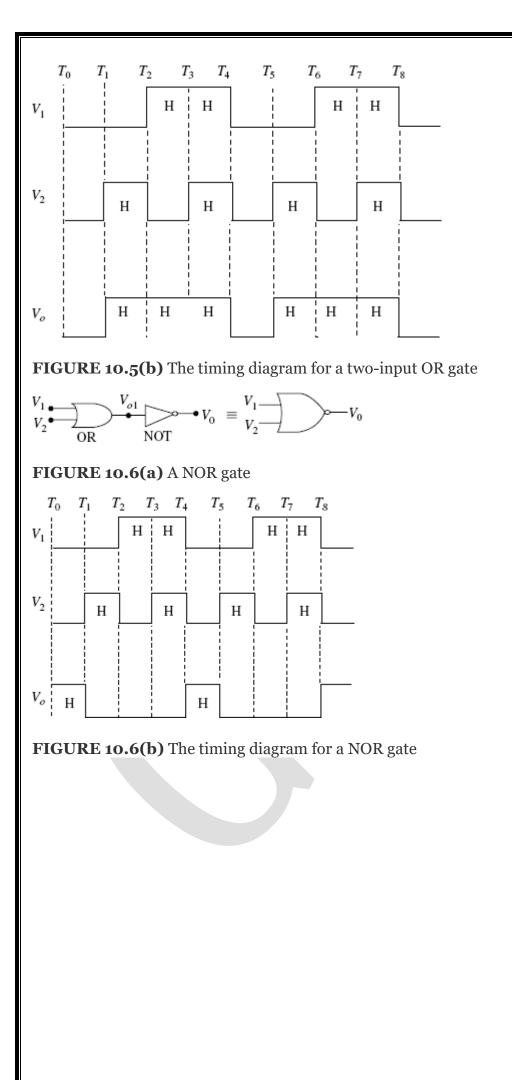

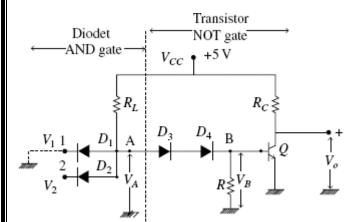

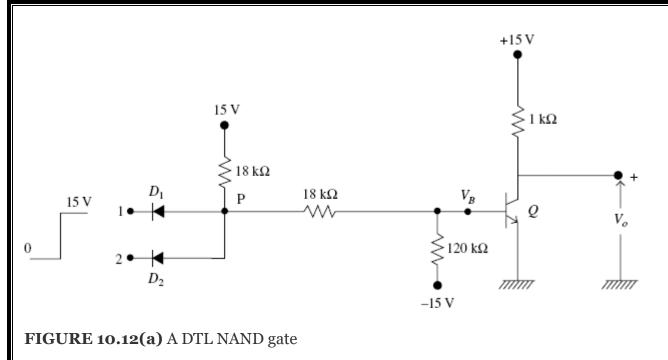

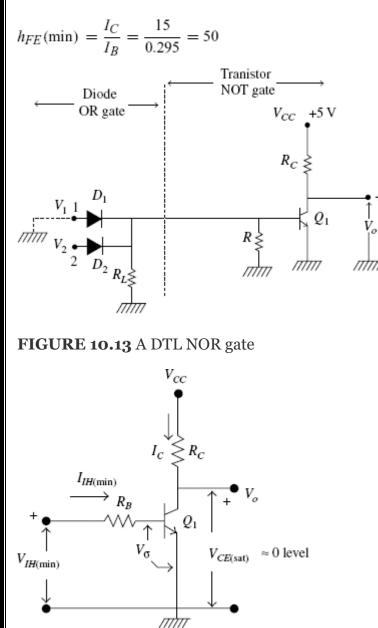

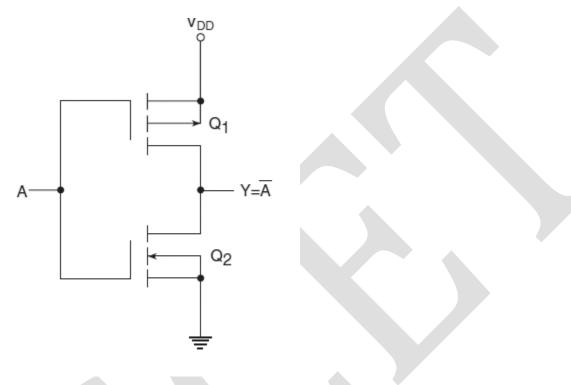

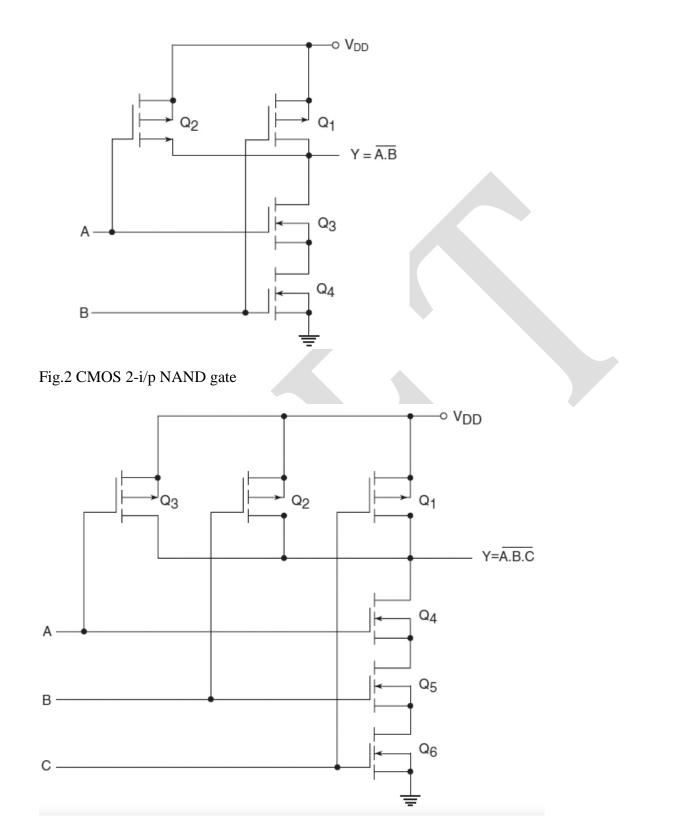

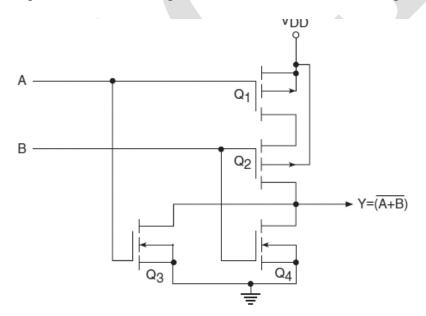

AND, OR and NOT gates using Diodes and Transistors, DCTL, RTL, DTL, TTL and CML Logic Families and its Comparison.

#### TEXT BOOKS

- 1. Millman's Pulse, Digital and Switching Waveforms J. Millman, H. Taub and Mothiki S Prakash Rao, 2<sup>nd</sup> ed. 2008, TMH

- 2. Solid State Pulse circuits David A. Bell, , 4th Edn., 2002 . PHI

#### REFERENCES

- a. Pulse and Digital Circuits -A. Anand Kumar, 205, PHI.

- b. Fundamentals of Pulse and digital Circuits Ronald J Tocci, 3 ed., 2008

- c. Pulse and digital Circuits Motheki S Prakash Rao, 2006, TMH.

- d. Wave Generation and Shaping L. Strauss.

## **3. VISION OF THE DEPARTMENT**

#### **Vision of the Department**

To impart quality technical education in Electronics and Communication Engineering emphasizing analysis,

design/synthesis and evaluation of hardware/ embedded software, using various Electronic Design Automation (EDA)

tools with accent on creativity, innovation and research thereby producing competent engineers who can meet global

challenges with societal commitment.

#### 4. MISSION OF THE DEPATMENT

#### **Mission of the Department**

- To impart quality education in fundamentals of basic sciences, mathematics, electronics and communication engineering through innovative teaching-learning processes.

- To facilitate Graduates define, design, and solve engineering problems in the field of Electronics and Communication Engineering using various Electronic Design Automation (EDA) tools.

- To encourage research culture among faculty and students thereby facilitating them to be creative and innovative through constant interaction with R & D organizations and Industry.

- To inculcate teamwork, imbibe leadership qualities, professional ethics and social responsibilities in students and faculty.

## 5. PEO's and PO's

## Program Educational Objectives of B. Tech (ECE) Program

- PEO-1:To prepare students with excellent comprehension of basic sciences, mathematics and engineering subjects facilitating them to gain employment or pursue higher studies with an appreciation for lifelong learning.

- PEO-2:To train students with problem solving capabilities such as analysis and design with adequate practical skills wherein they demonstrate creativity and innovation that would enable them to develop state of the art equipment and technologies of multidisciplinary nature for societal development.

- PEO-3:To inculcate positive attitude, professional ethics, effective communication and interpersonal skills which would facilitate them to succeed in the chosen profession exhibiting creativity and innovation through research and development both as team member and as well as leader.

## **PROGRAM OUTCOMES (ECE)**

1.An ability to apply knowledge of Mathematics, Science, and Engineering to solve complex engineering problems of Electronics and Communication Engineering systems.

2.An ability to model, simulate and design Electronics and Communication Engineering systems, conduct experiments, as well as analyze and interpret data and prepare a report with conclusions.

3.An ability to design an Electronics and Communication Engineering system, component, or process to meet desired needs within the realistic constraints such as economic, environmental, social, political, ethical, health and safety, Manufacturability and sustainability.

4.An ability to function on multidisciplinary teams involving interpersonal skills.

5.An ability to identify, formulate and solve engineering problems of multidisciplinary nature.

6.Understanding of professional and ethical responsibilities involved in the practice of Electronics and Communication Engineering profession.

7. Ability to communicate effectively with a range of audience on complex engineering problems of multidisciplinary nature both in oral and written form.

8. The broad education necessary to understand the impact of engineering solutions in a global, economic, environmental and societal context.

9. Recognition of the need for, and an ability to engage in life-long learning and acquire the capability for the same.

10.Knowledge of contemporary issues involved in the practice of Electronics and Communication Engineering profession

11.An ability to use the techniques, skills and modern engineering tools necessary for engineering practice.

12.An ability to use modern Electronic Design Automation (EDA) tools, software and electronic equipment to analyze, synthesize and evaluate Electronics and Communication Engineering systems for multidisciplinary tasks.

13. Apply engineering and project management principles to one's own work and also to manage projects of multidisciplinary nature.

## **<u>6. Course objectives and Outcomes</u>**

#### **COURSE OBJECTIVES:**

The main objectives of this course are:

- **CO** 1: Understand the applications of diode as Integrator, differentiator, clippers, clamper circuits.

- CO 2: Learn various switching devices such as diode, transistor, SCR.

- CO 3: Difference between logic gates and sampling gates.

- **CO 4:** Design Multivibrators for various applications, synchronization techniques and sweep circuits.

- **CO 5:** Realize logic gates using diodes and transistors.

#### **COURSE OUTCOMES:**

#### At the end of the course, the student will be able to:

CO1: Understand the applications of diode as Integrator, differentiator, clippers, clamper circuits.

CO2: Learn various switching devices such as diode, transistor, SCR.

CO3: Difference between logic gates and sampling gates

CO4: Design Multivibrators for various applications, synchronization techniques and sweep circuits

CO5: Realize logic gates using diodes and transistors.

## 7. Brief notes on the importance of the course and how it fits into the curriculum

This is the basic course for electronic engineers to understand the behavior of active and passive devices and circuit configurations used for the generation and processing of pulse, digital and switching waveforms. These non-sinusoidal signals find extensive application in fields such as computers, control systems, counting and timing systems, data-processing systems, digital instrumentation ,pulse communication, radar, telemetry, television and in many areas of experimental research. By studying this course students can understand better the courses in their future semesters such as control systems, IC Applications and Microprocessor and Microcontrollers.

## 8. Prerequisites if any

The following subject's knowledge is required for understanding the PDC course.

1. Electronic Devices and Circuits 2. Electric Circuits 3. STLD.

9. Instructional Learning Outcomes

## Instructional objectives and learning outcomes

## Instructional Unit-wise objectives

- 1. To study and analyze linear wave shaping circuits such as R-C and R-L-C transient circuits .

- 2. To study and analyze non-linear wave shaping circuits such as clippers, clampers and comparators.

- 3. To study the switching characteristics of diode, transistor and SCR.

- 4. To study the operating principles of various sampling gates.

- 5. To design and analyze various multivibrators using transistors.

- 6. To design and analyze time base generators

- 7. To design and analyze various sweep circuits.

- 8. To discuss and realize logic gates using diodes and transistors

## **Instructional objectives**

## **Unit 1: Linear Wave Shaping**

- To study about linear wave shaping circuits and Non-linear wave shaping circuits for different input signals.

- To describe the application of a low pass circuit as an integrator.

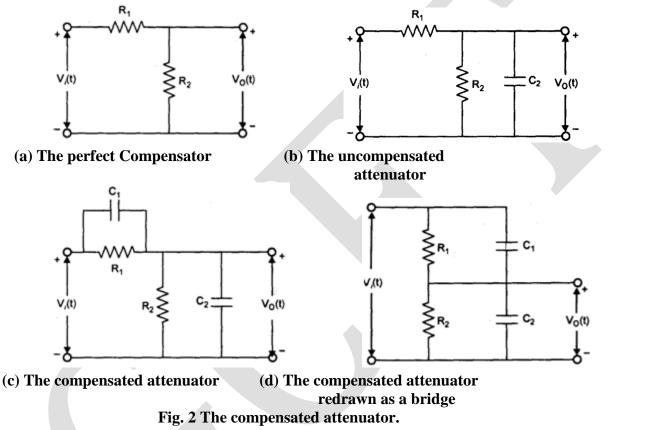

- To understand the principles of working of uncompensated and compensated attenuators and the operation of the attenuator circuit in CRO probe.

- To derive the response of high pass RC, RL and RLC circuits to different types of inputs like Sinusoidal, pulse, step, square, ramp and exponential inputs.

- To describe the application of high pass circuit as Differentiator.

- To understand the operation of the ringing circuit.

## Unit 2: Non-linear Wave Shaping

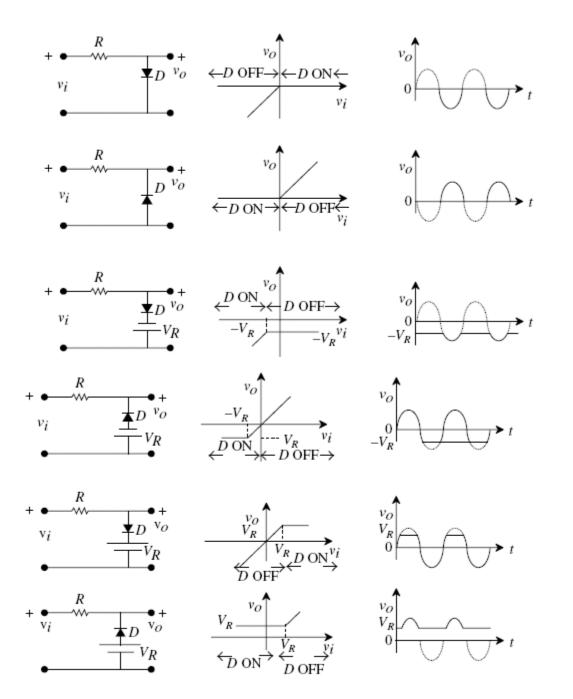

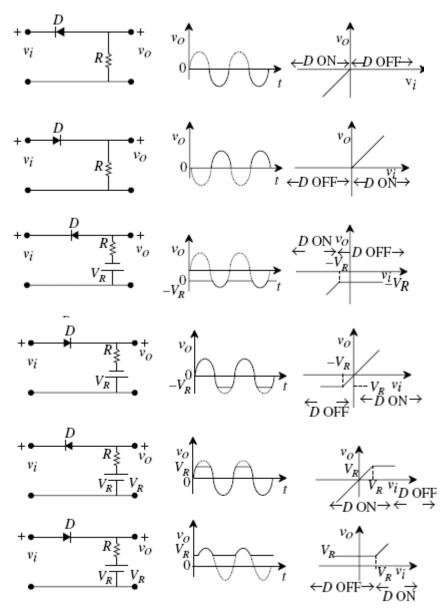

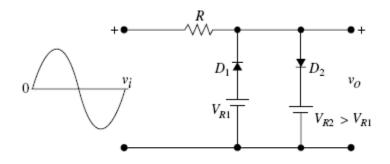

- To study the principle of operation of various series and shunt clipping circuits

- To study about diode comparators and double differentiators as amplitude comparators and it's applications .

- To study the principle of operation of various clamping circuits and verify the clamping circuit theorem.

- To derive the necessary relations to plot steady state output.

- To describe the effect of diode characteristics on the clamping voltage.

- To describe synchronized clamping.

## **Unit 3: Switching characteristics of Devices:**

- To study the principle of operation of diodes and transistors as switches.

- To study the effect of inter-electrode capacitances on switching times.

- To study the switching times of devices and derive the necessary relations.

- To study the temperature dependence of the transistor on various parameters.

- To understand the use of transistor switch as latch.

- To realize the use of transistor switches with inductive and capacitive loads.

- To study the principle of operation of switching circuits using SCS.

- To understand the working of unidirectional and bidirectional sampling gates and their variations

- To understand the working of sampling gates using Diodes (two, four and six) and transistors.

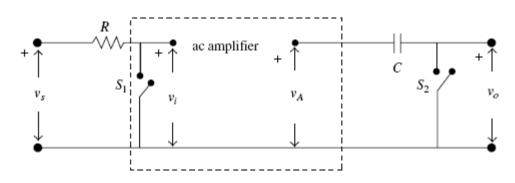

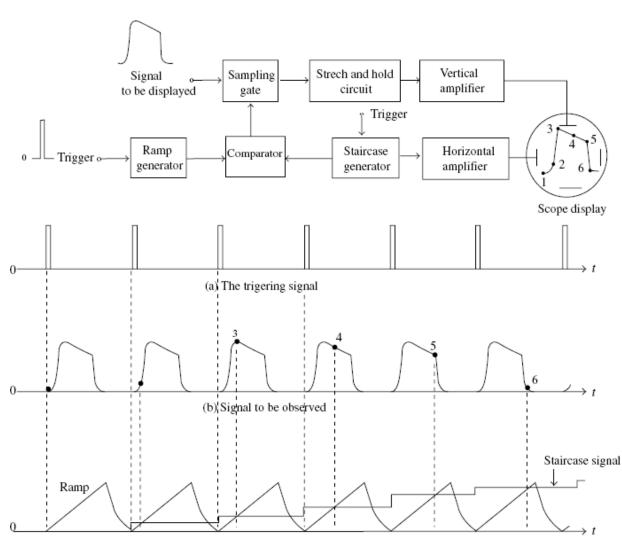

- To realize the applications of sampling gates in sampling scope

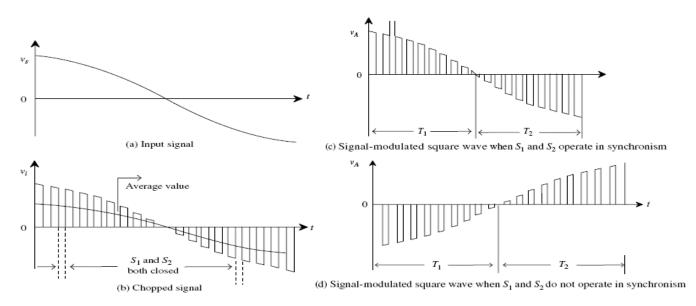

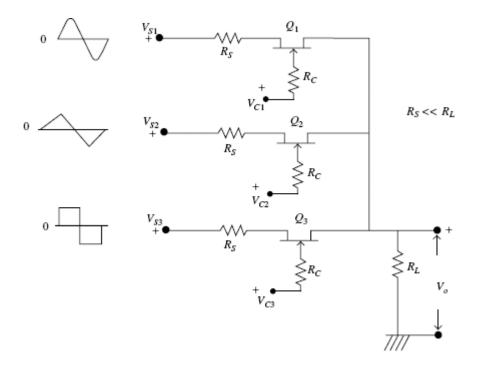

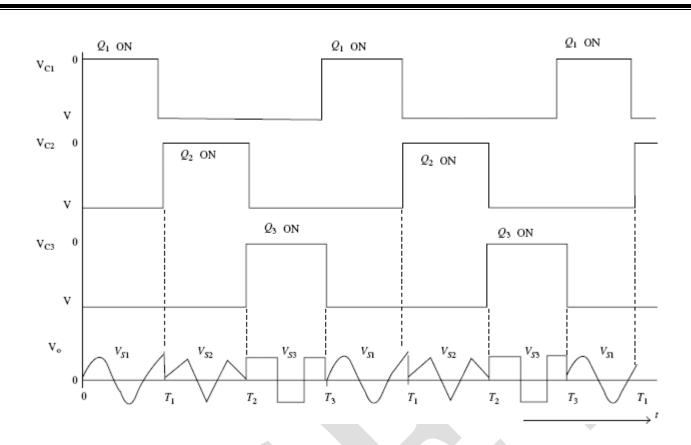

- To derive a choppers stabilized amplifier using sampling gates

## Unit 4: Multivibratos

- To study the principle of operation of the multivibrators.

- To study the applications of multivibrators.

- To realize the need for a commutating condenser in a monostable multivibrator and bistable multivibrator.

- To study the principle of operation of Time base generators

- To study the features of the Time base signal.

- To study the principle of operation of Miller Time base

- To study the principle of operation of Bootstrap Time base generator

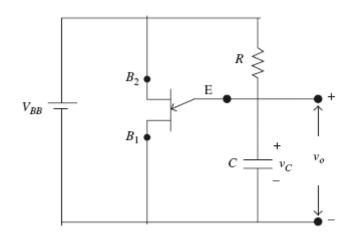

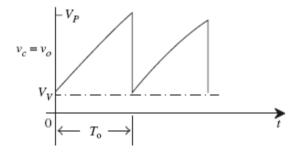

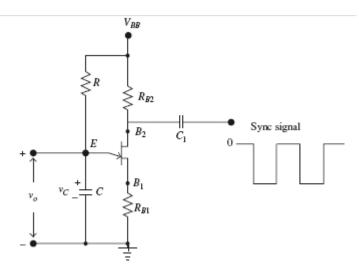

- To study the principle of operation of UJT saw tooth generator.

- To study the principle of operation of time base generators using Op-Amps.

## **Unit 5: Synchronization and frequency division**

- To study the operation of synchronization and frequency division circuits..

- To describe the methods of achieving frequency synchronization and division in other relaxation circuits like astable and monostable multivibratos

- To realize the circuit that eliminates jitter in a relaxation divider

- To understand the principle of operation of the circuits that achieve frequency synchronization and division using symmetric circuits

## **Realization of logic gates using Diodes and Transistors**

• To understand the principle of operation of basic logic gates like AND, OR and NOT gates

- To implement these gates using Diodes and Transistors

- To understand the various logic families like DCTL, RTL, DTL, TTL and CML and their comparison

- To implement simple Boolean functions using different logic families.

## **Student Learning Outcomes**

## Unit 1: Linear Wave Shaping

#### After completing this unit, the students are able to

- Design linear wave shaping circuits using linear elements like R C and L.

- Derive the expressions and plot the response of low pass RC circuits to different types of inputs namely sinusoidal, step, pulse, square-wave, exponential and ramp.

- Describe the application of a low pass circuit as an integrator.

- Understand the principles of working of uncompensated and compensated attenuators and the operation of the attenuator circuit in CRO probe.

- Derive the response of high pass RC and RL circuits to different types of inputs like Sinusoidal, pulse, step, square, ramp and exponential inputs.

- Describe the application of high pass circuit as Differentiator.

- Understand the operation of the ringing circuit.

- Find the response of RL and RLC circuits to step input.

## **Unit 2: Non-linear Wave Shaping**

#### After completing this unit, the students are able to

- Design various series and shunt clipping circuits and their combinations.

- Understand the principle of operation of two level emitter coupled transistor clippers and noise clippers

- Describe simple diode comparators and double differentiators as amplitude comparators.

- Explain the applications of comparators.

- Design various clamping circuits and verify the clamping circuit theorem.

- Derive the necessary relations to plot steady state output.

- Describe the effect of diode characteristics on the clamping voltage.

- Describe synchronized clamping.

- State and derive the clamping circuit theorem

## Unit 3: Switching characteristics of Devices and sampling gates

#### After completing this unit, the students are able to

- Use diodes and transistors as switches.

- Describe the effect of inter-electrode capacitances on switching times.

- Describe the switching times of devices and derive the necessary relations.

- Describe the temperature dependence of the transistor on various parameters.

- Understand the use of transistor switch as latch.

- Realize the use of transistor switches with inductive and capacitive loads.

- Design switching circuits using SCS.

- Understand the working of unidirectional and bidirectional sampling gates and their variations

- Design sampling gates using Diodes (two, four and six) and transistors.

- Describe the output by adjusting the levels of the control signal

- Realize the applications of sampling gates in sampling scope

- Derive a choppers stabilized amplifier using sampling gates

## Unit 4: Multivibratos & Time Base Generators

#### After completing this unit, the students are able to

- Explain the principle of operation of the multivibrators.

- Analyze and design Bistable, Monostable and Astable multivibrators and able to calculate and frequency / pulse width of the generated signal.

- Plot the waveforms at various points in the circuit.

- Describe the emitter coupled astable multivibrators

- Use an astable multivibrator for applications such as voltage to frequency converter and frequency modulator

- Understand the working of emitter coupled monostable multivibrator

- Realize the need for a commutating condenser in a monostable multivibrator and bistable multivibrator.

- Realize the application of a monostable multivibrator as a voltage to time converter

- Analyze fixed bias and self bias bistable multivibrators

- Analyze and design emitter coupled bistable multivibrator, also called Schmitt trigger

- Describe the applications of bistable multivibrator circuits.

- Able to design different types of Time base generators

- Explain the features of the Time base signal.

- Design Miller Time base Generator and explain the principle of operation.

- Design Bootstrap Time base generator and explain the principle of operation.

- Design UJT saw tooth generator.

- Design current Time base generator.

- Design time base generators using Op-Amps.

# <u>Unit 5: Synchronization and frequency division & Realization of logic gates using Diodes and Transistors</u>

## After completing this unit, the students are able to

- Understand the principle of frequency synchronization using exponential methods like UJT relaxation oscillator circuit.

- Describe the methods of achieving frequency synchronization and division in other relaxation circuits like astable and monostable multivibratos

- Realize the circuit that eliminates jitter in a relaxation divider

- Understand the principle of operation of the circuits that achieve frequency synchronization and division using symmetric circuits

- Understand the principle of operation of basic logic gates like AND, OR and NOT gates

- Implement these gates using Diodes and Transistors

- Understand the various logic families like DCTL, RTL, DTL, TTL and CML and their comparison

- Able to implement simple Boolean functions using different logic families.

|                      |   |   |   | 10 | • Cou |   | appin |   |   |    | 1105 |    |    |    |

|----------------------|---|---|---|----|-------|---|-------|---|---|----|------|----|----|----|

| POs                  | 1 | 2 | 3 | 4  | 5     | 6 | 7     | 8 | 9 | 10 | 11   | 12 | 13 | 14 |

| Pulse and Digital    |   |   |   |    |       |   |       |   |   |    |      |    |    |    |

| circuits             |   |   |   |    |       |   |       |   |   |    |      |    |    |    |

| CO 1: Understand     | 2 | 2 | 2 |    | 2     |   |       | 1 | 1 |    | 2    |    |    | 1  |

| the applications of  |   |   |   |    |       |   |       |   |   |    |      |    |    |    |

| diode as Integrator, |   |   |   |    |       |   |       |   |   |    |      |    |    |    |

| differentiator,      |   |   |   |    |       |   |       |   |   |    |      |    |    |    |

| clippers, clamper    |   |   |   |    |       |   |       |   |   |    |      |    |    |    |

|                      |   |   |   |    |       |   |       |   |   |    |      |    |    |    |

## 10. Course mapping with PEOS and POs

| circuits.                                                                                                                 |   |   |   |   |  |   |   |   |  |   |

|---------------------------------------------------------------------------------------------------------------------------|---|---|---|---|--|---|---|---|--|---|

| <b>CO 2:</b> Learn various switching devices such as diode, transistor, SCR.                                              | 2 | 2 | 2 | 2 |  | 1 | 1 | 2 |  | 2 |

| CO 3: Difference                                                                                                          | 2 | 2 | 2 | 2 |  | 1 | 2 | 2 |  | 2 |

| between logic gates<br>and sampling gates                                                                                 |   |   |   |   |  |   |   |   |  |   |

| <b>CO 4:</b> Design<br>Multivibrators for<br>various applications,<br>synchronization<br>techniques and sweep<br>circuits | 1 | 2 | 2 | 2 |  | 1 | 2 | 2 |  | 2 |

| <b>CO 5:</b> Realize logic gates using diodes and transistors.                                                            | 1 | 2 | 2 | 2 |  | 1 | 2 | 2 |  | 2 |

## Mapping of Course with Programme Educational Objectives: (Sample)

| S.No | Course<br>component  | code   | course                           | Semester | PEO 1        | PEO 2        | PEO 3 |

|------|----------------------|--------|----------------------------------|----------|--------------|--------------|-------|

| 1    | Basic<br>Electronics | A40415 | Pulse and<br>Digital<br>circuits | 2        | $\checkmark$ | $\checkmark$ |       |

# **<u>11. Time table of concerned class</u>**

| Year/Sem/Sec: II-B. Te | ch-I Sem-A S    |                 |                 | ctronics & Communication<br>Room no.: LH-15 | in Englitee     |                 | ad Year 2014-15, V  | VEF: 29-12-2014 |

|------------------------|-----------------|-----------------|-----------------|---------------------------------------------|-----------------|-----------------|---------------------|-----------------|

| Class Incharge:        |                 |                 |                 | Room no.: Dir-15                            |                 |                 | au 1 cai 2014-15, 1 | 111.27-12-2014  |

| Time                   | 09.30-<br>10.20 | 10.20-<br>11.10 | 11.10-<br>12.00 | 12.00-12.50                                 | 12.50-<br>13.30 | 13.30-<br>14.20 | 14.20-15.10         | 15.10-16.00     |

| Period                 | 1               | 2               | 3               | 4                                           |                 | 5               | 6                   | 7               |

| Monday                 |                 |                 |                 |                                             |                 |                 |                     |                 |

| Tuesday                |                 |                 |                 |                                             | E               |                 |                     |                 |

| Wednesday              |                 |                 |                 |                                             | LUNCH           |                 |                     |                 |

| Thursday               |                 |                 |                 |                                             |                 |                 |                     |                 |

| Friday                 |                 |                 |                 |                                             | _               |                 |                     |                 |

| Saturday               |                 |                 |                 |                                             |                 |                 |                     |                 |

| No                     |                 | Subject(T/P)    | )               | Faculty N                                   | lame            |                 | Subject Code        | Periods/Week    |

| 1                      |                 |                 |                 |                                             |                 |                 |                     |                 |

| 2                      |                 |                 |                 |                                             |                 |                 |                     |                 |

|                        |                 |                 |                 |                                             |                 |                 |                     |                 |

| 3                                                                                                                                              |                            |                              |                  |                               |                         |                      |                                 |                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|------------------|-------------------------------|-------------------------|----------------------|---------------------------------|----------------------------------------------------|

| 4                                                                                                                                              |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 5                                                                                                                                              |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 6                                                                                                                                              |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 7                                                                                                                                              |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 1                                                                                                                                              |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 0                                                                                                                                              |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 8                                                                                                                                              |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 10                                                                                                                                             |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 10                                                                                                                                             |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 11                                                                                                                                             |                            |                              |                  | 1                             |                         |                      |                                 |                                                    |

| 12                                                                                                                                             |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| 13                                                                                                                                             |                            |                              |                  |                               |                         |                      |                                 |                                                    |

|                                                                                                                                                |                            |                              |                  |                               |                         |                      |                                 |                                                    |

| Year/Sem/Sec: II-B.Tech-                                                                                                                       | -I Sem-                    | D Section                    |                  | Room no: LH-18                |                         |                      | Aca<br>W                        | nd Year 2014-15,<br>VEF: 29-12-2014                |

|                                                                                                                                                |                            |                              |                  | Room no: LH-18                |                         |                      | W                               | nd Year 2014-15,<br>VEF: 29-12-2014                |

| Class Incharge:                                                                                                                                | -I Sem-<br>09.30-<br>10.20 | D Section<br>10.20-<br>11.10 | 11.10-12.00      | Room no: LH-18<br>12.00-12.50 | 12.50-<br>13.30         | 13.30-<br>14.20      | Aca<br>W<br>14.20-<br>15.10     | nd Year 2014-15,<br>VEF: 29-12-2014<br>15.10-16.00 |

| Class Incharge:<br>Time                                                                                                                        | 09.30-                     | 10.20-                       |                  |                               | 12.50-<br>13.30         | 13.30-<br>14.20<br>5 | 14.20-                          | VEF: 29-12-2014                                    |

| Class Incharge:<br>Time<br>Period                                                                                                              | 09.30-<br>10.20            | 10.20-<br>11.10              | 11.10-12.00      | 12.00-12.50                   | 12.50-<br>13.30         | 14.20                | 14.20-<br>15.10                 | VEF: 29-12-2014<br>15.10-16.00                     |

| Class Incharge:<br>Time<br>Period<br>Monday                                                                                                    | 09.30-<br>10.20            | 10.20-<br>11.10              | 11.10-12.00      | 12.00-12.50                   | 13.30                   | 14.20                | 14.20-<br>15.10                 | VEF: 29-12-2014<br>15.10-16.00                     |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday                                                                                         | 09.30-<br>10.20            | 10.20-<br>11.10              | 11.10-12.00      | 12.00-12.50                   | 13.30                   | 14.20                | 14.20-<br>15.10                 | VEF: 29-12-2014<br>15.10-16.00                     |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday                                                                | 09.30-<br>10.20            | 10.20-<br>11.10              | 11.10-12.00      | 12.00-12.50                   | 12.50-<br>13.30<br>HONN | 14.20                | 14.20-<br>15.10                 | VEF: 29-12-2014<br>15.10-16.00                     |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday                                                      | 09.30-<br>10.20            | 10.20-<br>11.10              | 11.10-12.00      | 12.00-12.50                   | 13.30                   | 14.20                | 14.20-<br>15.10                 | VEF: 29-12-2014<br>15.10-16.00                     |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday                                                      | 09.30-<br>10.20            | 10.20-<br>11.10              | 11.10-12.00      | 12.00-12.50                   | 13.30                   | 14.20                | 14.20-<br>15.10<br>6            | VEF: 29-12-2014<br>15.10-16.00                     |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday                                          | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00      | 12.00-12.50                   | 13.30<br>HONOT          | 14.20                | 14.20-<br>15.10                 | VEF: 29-12-2014<br>15.10-16.00                     |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday                                          | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONOT          | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday<br>No                                    | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday<br>No                                    | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday<br>No<br>1                               | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday<br>No<br>1                               | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time Period Monday Tuesday Wednesday Thursday Friday Saturday No 1 2 3                                                      | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday<br>No<br>1<br>2<br>3<br>4                | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday<br>No<br>1<br>2<br>3<br>4                | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time Period Monday Tuesday Wednesday Thursday Friday Saturday No 1 2 3 4 5 6                                                | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| Class Incharge:<br>Time<br>Period<br>Monday<br>Tuesday<br>Wednesday<br>Thursday<br>Friday<br>Saturday<br>No<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 09.30-<br>10.20            | 10.20-<br>11.10<br>2         | 11.10-12.00<br>3 | 4                             | 13.30<br>HONNIT         | 14.20                | 14.20-<br>15.10<br>6<br>Subject | VEF: 29-12-2014 15.10-16.00 7                      |

| 11                          |     |  |  |  |

|-----------------------------|-----|--|--|--|

|                             |     |  |  |  |

| 12                          |     |  |  |  |

| 13                          |     |  |  |  |

|                             |     |  |  |  |

|                             |     |  |  |  |

| * represents Tutorial class | ses |  |  |  |

## **<u>12. Individual time table</u>**

| Work Load: |   | W.E | .F: |    |   |   |    |     |

|------------|---|-----|-----|----|---|---|----|-----|

| Day/Hour   | Ι | II  | III | IV |   | V | VI | VII |

| MON        |   |     |     |    |   |   |    |     |

| TUE        |   |     |     |    | L |   |    |     |

| WED        |   |     |     |    | N |   |    |     |

| THU        |   |     |     |    | H |   |    |     |

| FRI        |   |     |     |    |   |   |    |     |

| SAT        |   |     |     |    |   |   |    |     |

PDC-II ECE- 2-2 A&D

## 13 .Lecture schedule with methodology being used/adopted

Department of Electronics & Communications Engineering

Year & Semesters to who subject is offered <u>II-II ECE (A, B,C & D)</u>

Name of the Subject: **Pulse and Digital and Circuits**

Name of the Faculty: **Prof. K.Somasekhara Rao** Designation: **Dean of Academics** Department: **ECE-section B**

Name of the Faculty: M.Muthamma Designation: Assistant Professor Department: ECE section-C

Name of the Faculty: V.Venkata lakshmi Designation: Assistant Professor Department: ECE section-A

Name of the Faculty: Subrahmanyam Designation: Assistant Professor Department: ECE section-D

## **13.1** Introduction to the Subject

This is the basic course for electronic engineers to understand the behavior of active and passive devices and circuit configurations used for the generation and processing of pulse, digital and switching waveforms.

These non-sinusoidal signals find extensive application in fields such as computers, control systems, counting and timing systems, data-processing systems, digital instrumentation ,pulse communication, radar, telemetry, television and in many areas of experimental research.

## 13.2 JNTU Syllabus with additional topics

| S.No. | Unit No. | Торіс                                                                         | Additional Topics               |

|-------|----------|-------------------------------------------------------------------------------|---------------------------------|

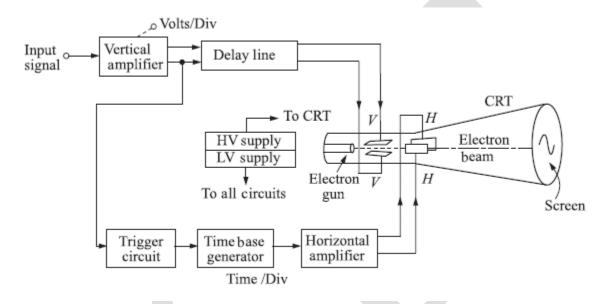

| 1     | Ι        | Linear wave shaping: High pass, low pass RC circuits                          | CRO operation and<br>CRO probes |

|       |          | High pass RC circuit response for sinusoidal and step inputs                  |                                 |

|       |          | High pass RC circuit response for ramp, pulse and square inputs               |                                 |

|       |          | Low pass RC circuit response for sinusoidal and step<br>inputs                |                                 |

|       |          | Low pass RC circuit response for ramp, pulse and square inputs                |                                 |

|       |          | High pass RC as an Differentiator and Low pass circuit as Integrator          |                                 |

|       |          | RL and RLC circuits and their response for step input,<br>Ringing circuit.    |                                 |

|       |          | Attenuators and its application as a CRO Probe                                |                                 |

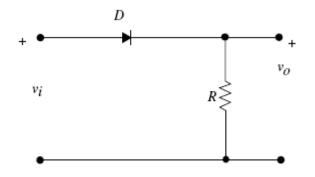

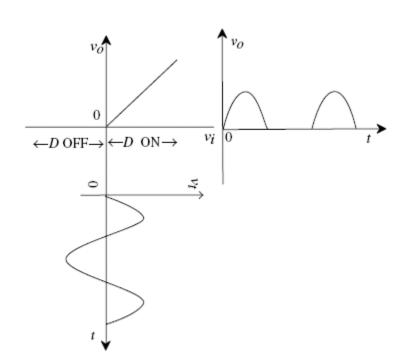

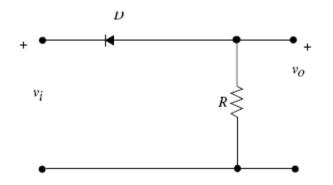

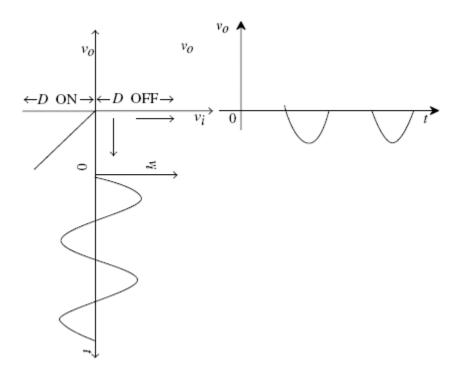

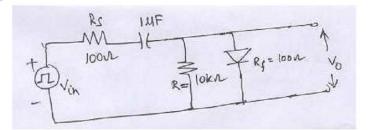

| 2     | П        | Non-linear wave shaping: Diode series clippers                                |                                 |

|       |          | Diode parallel clippers                                                       |                                 |

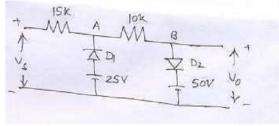

|       |          | Clipping at two independent levels                                            |                                 |

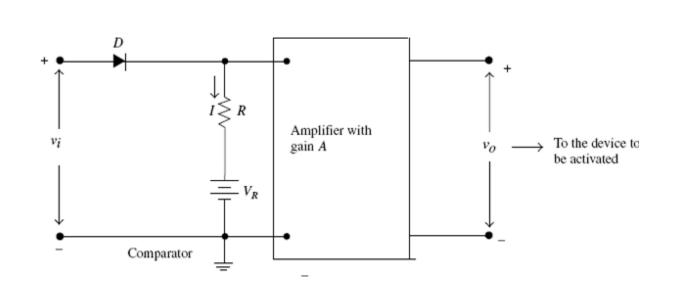

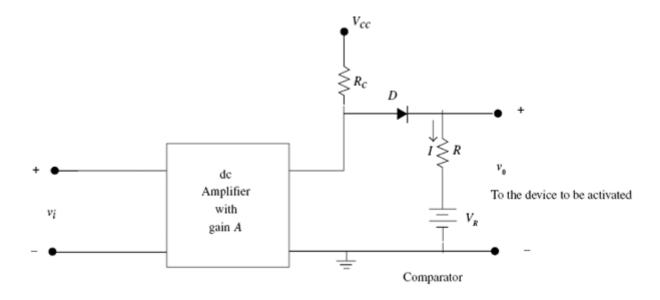

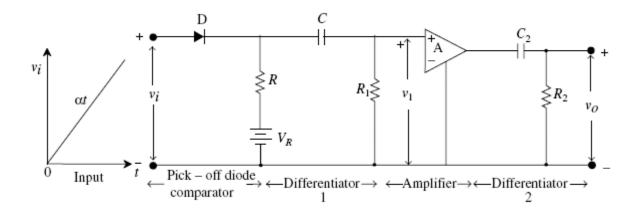

|       |          | Comparators, applications of voltage comparators                              |                                 |

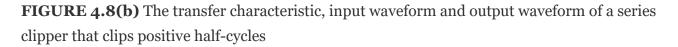

|       |          | Clamping operation                                                            |                                 |

|       |          | Clamping circuit taking Source and Diode resistance into account              |                                 |

|       |          | Clamping circuit theorem, practical clamping circuits                         |                                 |

|       |          | Effect of diode characteristics on clamping voltage,<br>Synchronized Clamping |                                 |

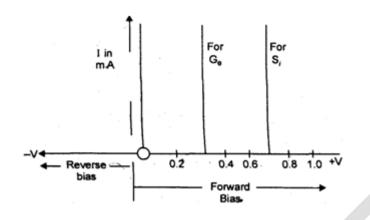

| 3     | III      | Switching characteristics of Devices: Diode as a                              |                                 |

|       |          | switch, piecewise linear diode characteristics                                |                                 |

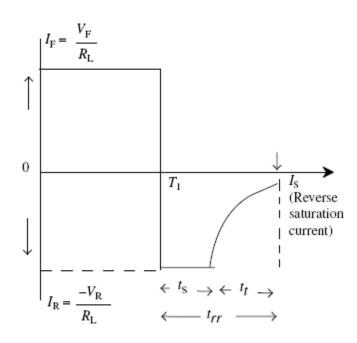

|       |          | Diode Switching times                                                         |                                 |

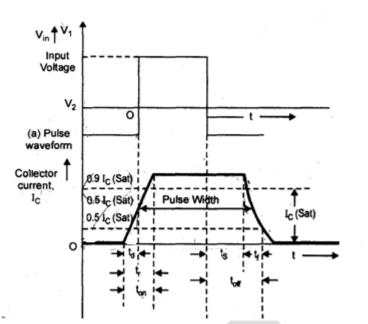

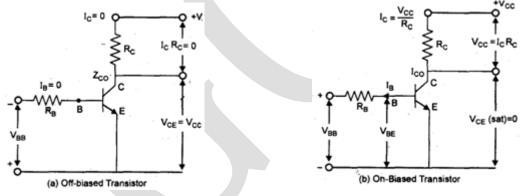

|       |          | Transistor as a switch                                                        |                                 |

|       |          | Break down voltage consideration of transistor                                |                                 |

|   |     | Saturation parameters of Transistor and their variation                                                       |                                   |

|---|-----|---------------------------------------------------------------------------------------------------------------|-----------------------------------|

|   |     | with temperature<br>Transistor switching times and Silicon controlled switch                                  |                                   |

|   |     | circuits                                                                                                      |                                   |

|   |     | MID-I                                                                                                         |                                   |

|   |     | Converting and an                                                                                             | 1                                 |

|   | III | Sampling gates:<br>Basic operating principles of sampling gates                                               |                                   |

|   |     | Unidirectional and Bi-directional sampling gates                                                              |                                   |

|   |     | Four diode and Six diode sampling gate                                                                        |                                   |

|   |     | Reduction of pedestal in gate circuits and Applications of sampling gate                                      |                                   |

| 4 | IV  | Multivibrators: Analysis of Bistable Multivibrator                                                            |                                   |

|   |     | Design of Bistable Multivibrator                                                                              |                                   |

|   |     | Analysis of Mono stable Multivibrator                                                                         |                                   |

|   |     | Design of Mono stable Multivibrator                                                                           |                                   |

|   |     | Analysis of Astable Multivibrator                                                                             |                                   |

|   |     | Design of Astable Multivibrator                                                                               |                                   |

|   |     | Applications of Multivibrators                                                                                |                                   |

|   |     | Triggering methods                                                                                            |                                   |

|   |     | Schmitt trigger                                                                                               | r                                 |

|   |     | Design Problems solving                                                                                       |                                   |

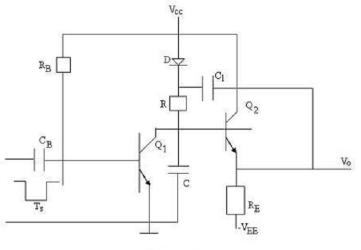

|   |     | <b>Time base generators:</b> General features of a time base signal, methods of generating time base waveform |                                   |

|   |     | Miller and Bootstrap time base generators – basic principle                                                   |                                   |

|   |     |                                                                                                               |                                   |

|   |     | Transistor miller time base generator                                                                         |                                   |

|   |     | Transistor Bootstrap time base generator                                                                      |                                   |

|   |     | UJT saw tooth wave generator<br>Current time base generators                                                  |                                   |

|   |     | _                                                                                                             |                                   |

| 5 | V   | Methods of linearity improvement                                                                              | CMOS and D!                       |

| 5 | v   | <b>Synchronization and frequency division:</b> Pulse Synchronization of Relaxation Devices                    | CMOS and Bi-<br>CMOS logic family |

|   |     | Frequency division in sweep circuit, Stability of<br>Relaxation Devices                                       |                                   |

| Astable relaxation circuits, Monostable relaxation circuits                            |  |

|----------------------------------------------------------------------------------------|--|

| Synchronization of a sweep circuit with symmetrical signals                            |  |

| Sine wave frequency division with a sweep circuit                                      |  |

| Realization of logic gates using Diodes and<br>Transistors: AND, OR gates using Diodes |  |

| AND, OR gates using Transistors DCTL,RTL                                               |  |

| DTL, TTL<br>CML logic families and its comparison                                      |  |

**13.3.** Source of Information

## **13.3.1 TEXT BOOKS:**

#### Suggested Text Books

- 1. Millman's Pulse, Digital and Switching Waveforms J. Millman and H. Taub and Mothiki S .Prakash Rao, 2 ed., 2008, TMH.

- 2. Solid State Pulse circuits David A. Bell, PHI, 4th Edn., 2002 PHI.

Reference Books:

## **13.3.2 REFERENCE BOOKS:**

- 13.3.2.1 Pulse and Digital Circuits A Anand Kumar, 2005, PHI

- 13.3.2.2 Fundamentals of Pulse and Digital Circuits Ronald Tocci, 3<sup>rd</sup> Ed, 2008

- 13.3.2.3 Pulse and Digital circuits Mothiki S Prakash Rao, 2006 TMH

- 13.3.2.4 Wave generation and Shaping L Strauss

## **13.3.3 WEBSITES**

- 1. en.wikipedia.org/wiki/Digital\_electronics

- 2. www.modernelectronics.org

- 3. www.electronicsforyou.com

- 4. <u>www.npteliitm.ac.in</u>

## 13.3.4 E-books

- 1. <u>http://www.youtube.com/watch?v=aO6tA1z933k</u>

- 2. <u>http://books.google.co.in/books?id=sxswmJgMbEsC&pg=PA118&lpg=PR16&ots=DXZAEipuZB&focus=viewport&dq=Pulse,+Digital+and+Switching+Waveforms+-+J.+Millman+and+H.+Taub#v=onepage&q=Pulse%2C%20Digital%20and%20Switching%20Waveforms%20-%20J.%20Millman%20and%20H.%20Taub&f=false</u>

## 13.3.5. JOURNALS

1. Nonsymmetric multivibrators with an auxiliary RC-circuit Filanovsky, I.M.; Piskarev, V.A.; Stromsmoe,

K.A. Electronic Circuits and Systems, IEE Proceedings G

Volume: 131, Issue: 4 Topic(s): Digital Object Identifier: 10.1049/ip-g-1:19840029

Publication Year: 1984, Page(s): 141 - 146

## 2. Combining 2-level logic families in grid-based nanoscale fabrics Teng Wang; Narayanan, P.; Moritz,

C.A. Nanoscale Architectures, 2007. NANOSARCH 2007. IEEE International Symposium on

Topic(s): Components, Circuits, Devices & Systems

## 3. Stability analysis of a digitally based HVDC firing-pulse synchronization control

Larsen, E.V.; Clark, K.; Lorden, D.J.

Power Delivery, IEEE Transactions on

## 13.4 MICRO PLAN:

<u>Sec –A</u>

| S.No. | Unit | Total  | Date | Topic to be covered in one lecture | Reg/Add | Teach | Remarks |

|-------|------|--------|------|------------------------------------|---------|-------|---------|

|       | No.  | no. of |      |                                    | itional | ing   |         |

|       |      | Period |      |                                    |         | aids  |         |

|       |      | S      |      |                                    |         | used  |         |

|    |    |    |                                          |          | LCD/   |

|----|----|----|------------------------------------------|----------|--------|

|    |    |    |                                          |          | OHP/   |

|    |    |    |                                          |          |        |

|    |    |    |                                          |          | BB     |

| 1  | Ι  | 10 | Linear wave shaping: High pass, low      | Regular  | BB     |

|    |    |    | pass RC circuits                         |          |        |

| 2  |    |    | High pass RC circuit response for        | Regular  | BB     |

|    |    |    | sinusoidal and step inputs               |          |        |

| 3  |    |    | High pass RC circuit response for        | Regular  | BB     |

|    |    |    | ramp, pulse and square inputs            |          |        |

| 4  |    |    | Low pass RC circuit response for         | Regular  | BB     |

|    |    |    | sinusoidal and step inputs               |          |        |

| 5  |    |    |                                          | Regular  | BB     |

|    |    |    | Low pass RC circuit response for         |          |        |

|    |    |    | ramp, pulse and square inputs            |          |        |

| 6  |    |    | High pass RC as an Differentiator        | Regular  | BB     |

|    |    |    | and Low pass circuit as Integrator       |          |        |

| 7  |    |    | RL and RLC circuits and their            | Regular  | BB     |

|    |    |    | response for step input, Ringing         |          |        |

|    |    |    | circuit. Attenuators and its application |          |        |

|    |    |    | as a CRO Probe                           |          |        |

| 8  |    |    | CRO operation and CRO probes             | Addition | Video  |

|    |    |    |                                          | al       | lectur |

|    |    |    |                                          |          | e      |

|    |    |    |                                          |          |        |

| 9  |    |    | Tutorial                                 | Regular  | BB     |

| 10 |    |    | Assignment Test                          |          | BB     |

| 11 | II | 10 | Non-linear wave shaping: Diode           | Regular  | BB/O   |

|    |    | -  | series clippers                          | Trogunar | HP     |

|    |    |    |                                          |          |        |

| 12 |    |    | Diode parallel clippers                  | Regular  | BB/    |

|    |    |    |                                          |          | ОНР    |

|    |    |    |                                          |          |        |

| 13 |    |    | Clipping at two independent levels       | Regular  | BB/    |

|    |    |    |                                          |          | OHP    |

|    |    |    |                                          |          |        |

| 14 |    |    | Comparators, applications of voltage     | Regular  | BB     |

|    |    |    | comparators                              |          |        |

| 15 |    |    | Clamping operation                       | Regular  | BB     |

| 16 |    |    | Clamping circuit taking Source and       | Regular  | BB     |

|    |    |    | Diode resistance into account            | 8        |        |

| 17 |    |    | Clamping circuit theorem, practical      | Regular  | BB     |

|    |    |    | clamping circuits                        | 8        |        |

| 18 |       |    |   | Effect of diode characteristics on clamping voltage, Synchronized                | Regular  | BB/        |  |  |

|----|-------|----|---|----------------------------------------------------------------------------------|----------|------------|--|--|

|    |       |    |   | Clamping                                                                         |          | OHP        |  |  |

| 19 |       |    |   | Tutorial                                                                         | Regular  | BB         |  |  |

| 20 |       |    |   | Assignment Test                                                                  |          | BB         |  |  |

| 21 | III   | 11 | - | Switching characteristics of                                                     | Regular  | BB         |  |  |

|    |       |    |   | <b><u>Devices:</u></b> Diode as a switch, piecewise linear diode characteristics |          |            |  |  |

| 22 |       |    |   | Diode Switching times                                                            | Regular  | BB         |  |  |

| 23 |       |    | + | Transistor as a switch,                                                          | Regular  | BB         |  |  |

|    |       |    |   | Break down voltage consideration of transistor                                   |          |            |  |  |

| 24 |       |    | 1 | Saturation parameters of Transistor                                              | Regular  | BB         |  |  |

|    |       |    |   | and their variation with temperature                                             |          |            |  |  |

| 25 |       |    | + | Transistor switching times and Silicon                                           | Regular/ | BB         |  |  |

|    |       |    |   | controlled switch circuits                                                       | ОНР      |            |  |  |

| 26 | MID-I |    |   |                                                                                  |          |            |  |  |

| 27 | III   |    |   | Sampling gates:                                                                  | Regular  | BB/O       |  |  |

|    |       |    |   | Basic operating principles of sampling gates                                     |          | HP         |  |  |

| 28 |       |    |   | Unidirectional and Bi-directional sampling gates                                 | Regular  | BB         |  |  |

| 29 |       |    |   | Four diode and Six diode sampling gate                                           | Regular  | BB         |  |  |

| 30 |       |    |   | Reduction of pedestal in gate circuits<br>and Applications of sampling gate      | Regular  | BB         |  |  |

| 31 |       |    |   | Tutorial                                                                         | Regular  | BB         |  |  |

| 32 |       |    |   | Assignment Test                                                                  | Regular  | BB         |  |  |

| 33 | IV    |    |   | Multivibrators: Analysis of<br>Bistable Multivibrator                            | Regular  | BB/O<br>HP |  |  |

| 34 |       |    |   | Design of Bistable Multivibrator                                                 | Regular  | BB/O<br>HP |  |  |

| 35 |       |    |   | Analysis of Mono stable Multivibrator<br>Design of Mono stable Multivibrator     | Regular  | BB/O<br>HP |  |  |

| 36 |       |    |   | Analysis of Astable Multivibrator<br>Design of Astable Multivibrator             | Regular  | BB/O       |  |  |

|    |   |  |                                                                                                               |         | HP                   |  |

|----|---|--|---------------------------------------------------------------------------------------------------------------|---------|----------------------|--|

| 37 |   |  | Applications of Multivibrators                                                                                | Regular | Video<br>lectur<br>e |  |

| 38 |   |  | Triggering methods                                                                                            | Regular | BB                   |  |

| 39 |   |  | Schmitt trigger                                                                                               | Regular | BB                   |  |

| 40 |   |  | Design Problems solving                                                                                       | Regular | BB                   |  |

| 41 |   |  | Tutorial                                                                                                      | Regular | BB                   |  |

| 42 |   |  | <b>Time base generators:</b> General features of a time base signal, methods of generating time base waveform | Regular | BB                   |  |

| 43 |   |  | Miller and Bootstrap time base<br>generators – basic principle                                                | Regular | BB                   |  |

| 44 |   |  | Transistor miller time base generator                                                                         | Regular | BB/O<br>HP           |  |

| 45 |   |  | Transistor Bootstrap time base generator                                                                      | Regular | BB/O<br>HP           |  |

| 46 |   |  | UJT saw tooth wave generator                                                                                  | Regular | BB/O<br>HP           |  |

| 47 |   |  | Current time base generators<br>Methods of linearity improvement                                              | Regular | BB/O<br>HP           |  |

| 48 |   |  | Tutorial                                                                                                      | Regular | BB/O<br>HP           |  |

| 49 |   |  | Assignment Test                                                                                               | Regular | BB                   |  |

| 50 |   |  | <b>Synchronization and frequency</b><br><b>division:</b> Pulse Synchronization of<br>Relaxation Devices       | Regular | BB                   |  |

| 51 | V |  | Frequency division in sweep circuit,<br>Stability of Relaxation Devices                                       |         | BB                   |  |

| 52 |   |  | Astable relaxation circuits, Monostable relaxation circuits                                                   |         | BB                   |  |

| 53 | Synchronization of a sweep circuit<br>with symmetrical signals                                            |         | BB         |

|----|-----------------------------------------------------------------------------------------------------------|---------|------------|

| 54 | Sine wave frequency division with a sweep circuit                                                         | Regular | BB         |

| 55 | Realization of logic gates using<br>Diodes and Transistors: AND, OR<br>gates using Diodes and Transistors | Regular | BB/L<br>CD |

| 56 | DCTL,RTL, DTL, TTL                                                                                        | Regular | BB/L<br>CD |

| 57 | CMOS and Bi-CMOS logic<br>family                                                                          | Regular | BB/L<br>CD |

| 58 | CML logic families and its comparison                                                                     | Regular | BB/L<br>CD |

| 59 | Tutorial                                                                                                  | Regular | BB         |

| 60 | Assignment Test                                                                                           | Regular | BB         |

| 61 | Revision                                                                                                  | Regular | BB         |

| 62 | MID-II                                                                                                    | Regular | BB         |

## 13.5. Subject Contents

13.5. 1. Synopsis page for each period(62 pages)

- 13.5.2. Detailed Lecture notes containing:

- 1. PPTs

- 2. OHP slides

- 3. Subjective type questions (approximately 5 to 8 in no)

- 4. Objective type questions (approximately 20 to 30 in no)

- 5. Any simulations

## **13.6.** Course Review (By the concerned Faculty):

(I)Aims

(II) Sample check

| (III) End of the course report by the concerned faculty             |                 |

|---------------------------------------------------------------------|-----------------|

| GUIDELINES:                                                         |                 |

| Distribution of periods:                                            |                 |

| No. of classes required to cover JNTU syllabus                      | : 44            |

| No. of classes required to cover Additional topics                  | : 2             |

| No. of classes required to cover Assignment tests (for every 1 unit | its 1 test) : 5 |

| No. of classes required to cover tutorials                          | : 6             |

| No. of classes required to cover Mid tests                          | : 2             |

| No of classes required to solve University                          | : 3             |

| Question papers                                                     |                 |

|                                                                     |                 |

| Total no of p                                                       | eriods :62      |

|                                                                     |                 |

| <u>14 .Detailed not</u>                                             | <u>es</u>       |

| <u>UNIT- I</u>                                                      |                 |

## **1. INTRODUCTION**

Linear network: Circuit designed with linear elements Resistors, Capacitor and Inductors is called linear network.

Linear elements :Resistor ,capacitors and inductors are called linear elements because the current passing to the elements is proportional to the applied voltage, there is a linear relation between current and voltage.

When a sinusoidal signal applied to linear network the output also sinusoidal in nature but a non-sinusoidal signal response is different.

When devices such as diodes, bipolar junction transistors (BJTs) and field-effect transistors (FETs) are used in amplifiers, oscillators, rectifiers and other such applications, these devices are used either as linear or nonlinear circuit elements, for which they have to be used in a limited range of the transfer characteristic (defines the relation between the input and the output). If the operation goes beyond the

linear region of the transfer characteristic, unwanted frequencies called harmonics—integer multiples of the fundamental frequency—appear in the output of the circuit. However, when the signal swing is large, as in power amplifiers, the output is invariably distorted. This distortion can be minimized using a push—pull configuration as this arrangement eliminates even harmonics. To analyze a given circuit comprising such devices, it is possible to replace the device by its equivalent circuit. To simplify the analysis, it is necessary, at times, to piece-wise linearize the transfer characteristic so that the behavior of the device can be predicted in that limited region of operation.

These devices—diodes, transistors, FETs and so on—can also be used as switches in switching applications by driving the device into the OFF state in one case and by driving the device into the ON state in the other case. However, the inter-electrode capacitances limit the switching speed. Operational amplifiers and negative resistance devices also find applications in pulse and switching circuits. This chapter presents a brief overview of the fundamentals to facilitate comprehension of the principles of pulse and switching circuits.

#### **1.2 CURRENT AND VOLTAGE SOURCES**

Normally either ac or dc sources are used as current and voltage sources. A source can be either a voltage source (Thévenin source) or a current source (Norton source). An ideal voltage source should have zero internal resistance so that when current is drawn from the source, there is no voltage drop across the internal resistance of the source and the entire source voltage is available at its output terminals. Similarly, in a current source, no appreciable amount of current should flow through the internal resistance of the generator and the entire source current should flow through the load. For this, the internal resistance of the current source should ideally be infinity.

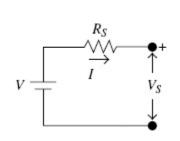

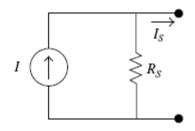

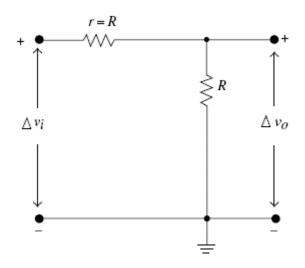

<u>Figure 1.1(a)</u> shows a practical voltage or Thévenin source and <u>Fig. 1.1(b)</u> a current or Norton source. It is possible to convert a Thévenin source into a Norton source and vice versa. To convert the Thévenin source [represented in <u>Fig. 1.1(a)</u>] into a Norton source [see <u>Fig. 1.1(b)</u>], we calculate the current (*I*) in the circuit using the relation  $I = V/R_s$ , where  $R_s$  is the internal resistance in shunt with the current source *I*. Similarly, to convert the Norton source into a Thévenin source as shown in <u>Fig. 1.1(a)</u>, we calculate the voltage (*V*) across  $R_s$  as  $V = IR_s$ , where  $R_s$  is its internal resistance in series with the source *V*. Consider the single-loop network using a voltage source, as shown in <u>Fig. 1.2</u>. From <u>Fig. 1.2</u>:

FIGURE 1.1(a) Thévenin or voltage source

FIGURE 1.1(b) Norton or current source

$$I = \frac{V}{R_1 + R_2}$$

and

$$V_{R2} = IR_2 = \frac{VR_2}{R_1 + R_2}$$

The single-loop network shown in Fig. 1.2 is analyzed using Ohm's law. In this circuit,  $R_1$  and  $R_2$  comprise a potential divider. So, Eq. (1.1) is used to calculate  $V_{R_2}$  directly instead of first calculating the current and then the voltage.

However, to analyze a network that has more than one loop, i.e., calculate the current in a given loop or voltage across the given branch, two basic network theorems—Kirchoff's voltage law and Kirchoff's current law—are used.

## FIGURE 1.2 A single-loop network

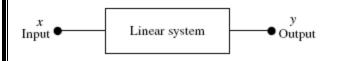

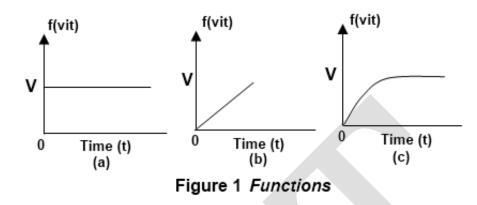

Linear systems are those that satisfy both homogeneity and additivity.

(i) Homogeneity: Let *x* be the input to a linear system and *y* the corresponding output, as shown in Fig. 2.1. If the input is doubled (2*x*), then the output is also doubled (2*y*). In general, a system is said to exhibit homogeneity if, for the input *nx* to the system, the corresponding output is *ny* (where *n* is an integer). Thus, a linear system enables us to predict the output.

FIGURE 2.1 A linear system

(ii) Additivity: For two input signals  $x_1$  and  $x_2$  applied to a linear system, let  $y_1$  and  $y_2$  be the corresponding output signals. Further, if  $(x_1 + x_2)$  is the input to the linear system and  $(y_1 + y_2)$  the corresponding output, it means that the measured response will just be the sum of its responses to each of the inputs presented separately. This property is called additivity. Homogeneity and additivity, taken together, comprise the principle of superposition.

(iii) Shift invariance: Let an input x be applied to a linear system at time  $t_1$ . If the same input is applied at a different time instant  $t_2$ , the two outputs should be the same except for the corresponding shift in time. A linear system that exhibits this property is called a shift-invariant linear system. All linear systems are not necessarily shift invariant.

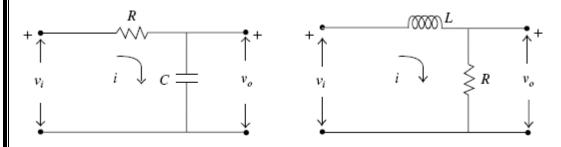

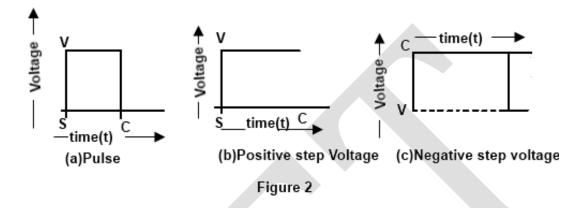

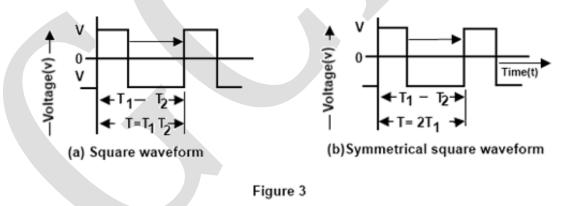

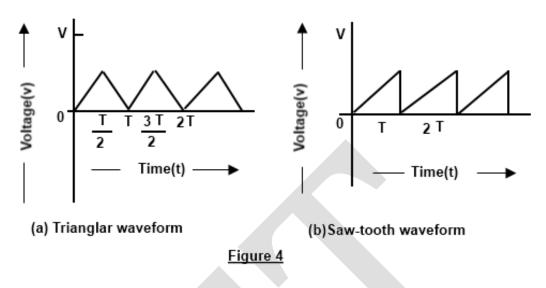

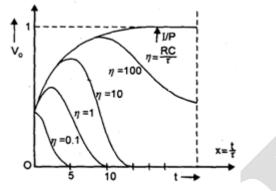

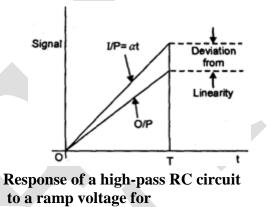

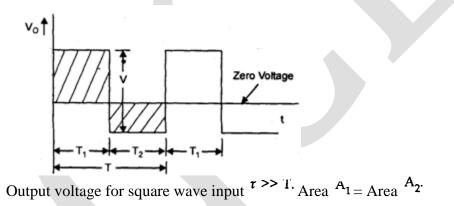

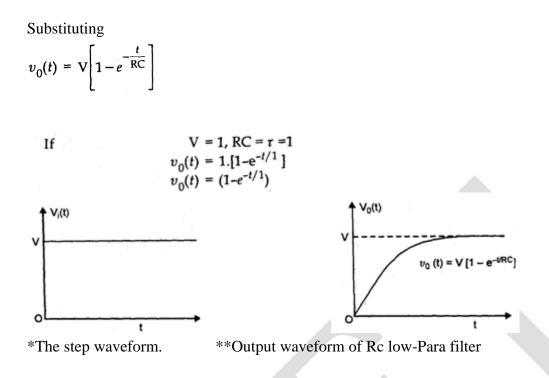

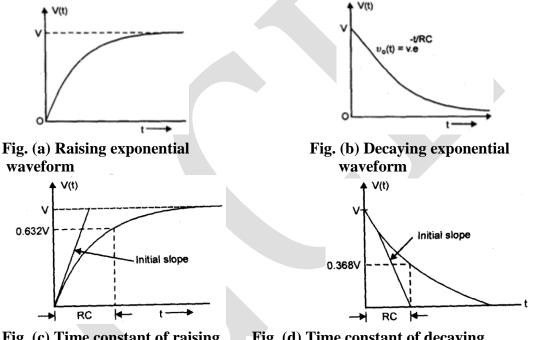

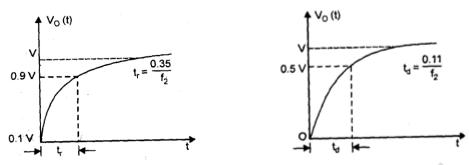

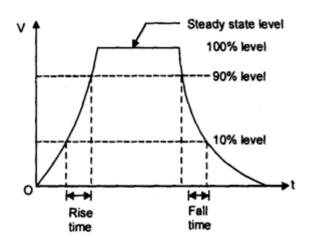

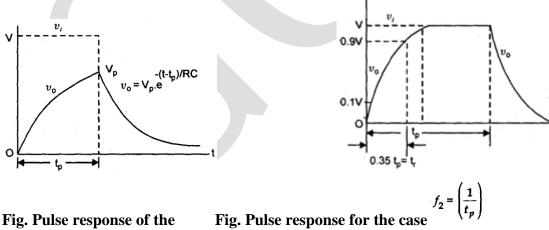

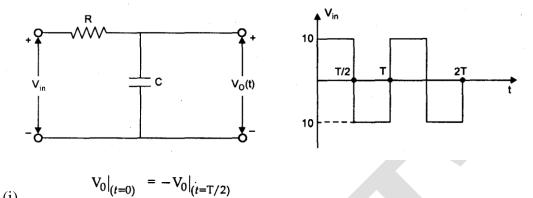

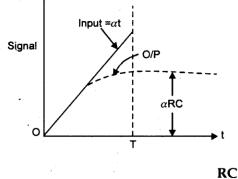

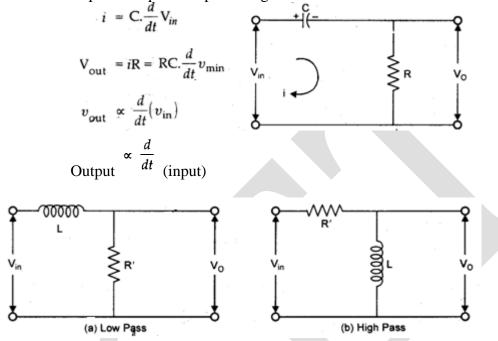

A circuit employing linear circuit components, namely, *R*, *L* and *C* can be termed a linear circuit. When a sinusoidal signal is applied to either *RC* or *RL* circuits, the shape of the signal is preserved at the output, with a change in only the amplitude and the phase. However, when a non-sinusoidal signal is transmitted through a linear network, the form of the output signal is altered. The process by which the shape of a non-sinusoidal signal passed through a linear network is altered is called linear waveshaping. We study the response of high-pass *RC* and*RL* circuits to different types of inputs in the following sections.

## **2.2 HIGH-PASS CIRCUITS**

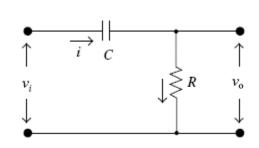

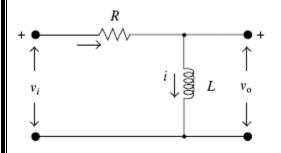

Figures 2.2(a) and 2.2(b) represent high-pass RC and RL circuits, respectively.

## FIGURE 2.2(a) A high-pass RC circuit